Method and article of manufacture to generate IC test vector for synchronized physical probing

a technology of physical probing and test pattern, applied in the direction of electronic circuit testing, measurement devices, instruments, etc., can solve the problems of insufficient complete localization, inability to complete localization, and inability to directly mechanically probe on-die electrical signals, and achieve the effect of efficient introduction of care-bit patterns

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033]Unless defined otherwise, all technical and scientific terms used herein have a meaning consistent with a common understanding of those of ordinary skill in the art(s) to which this invention belongs.

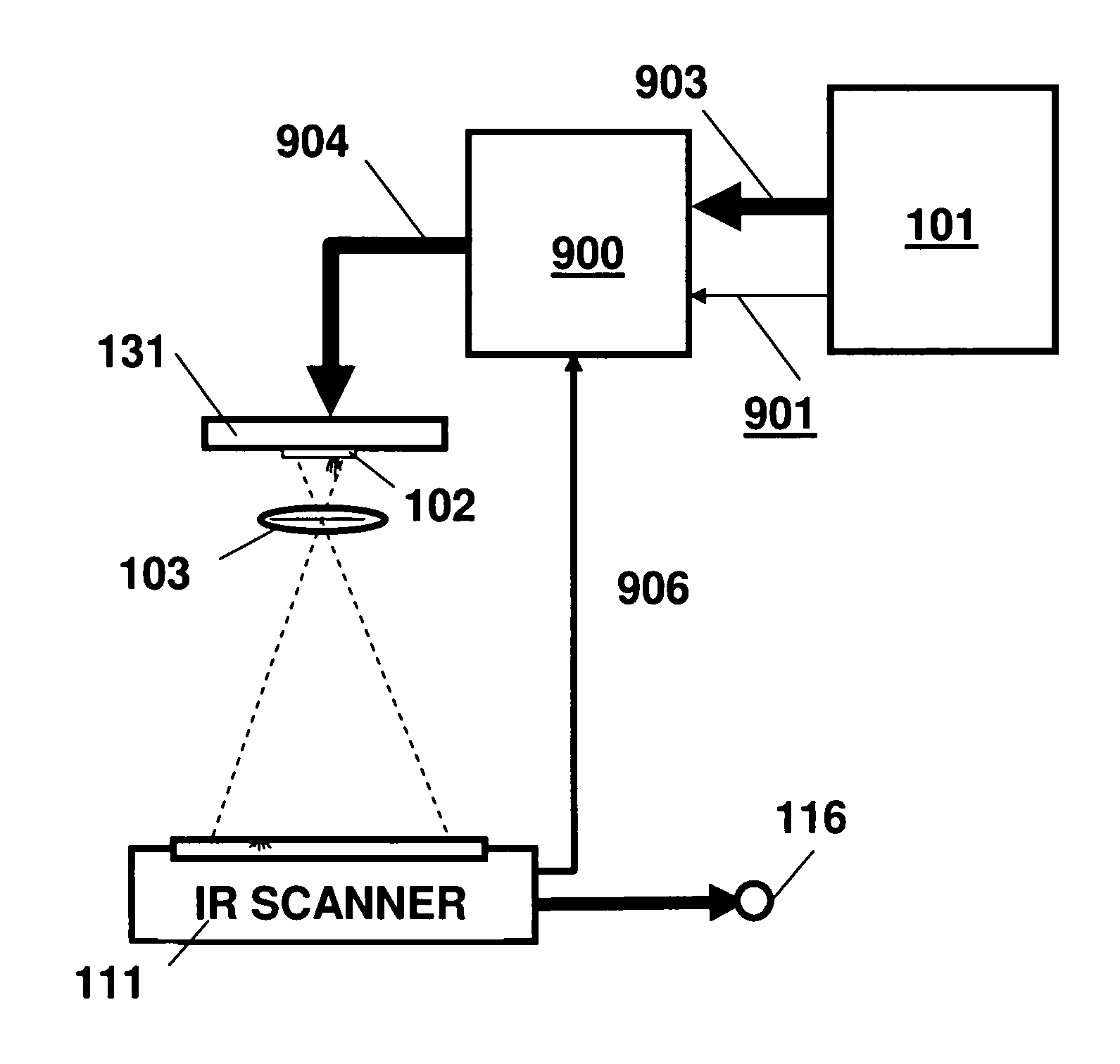

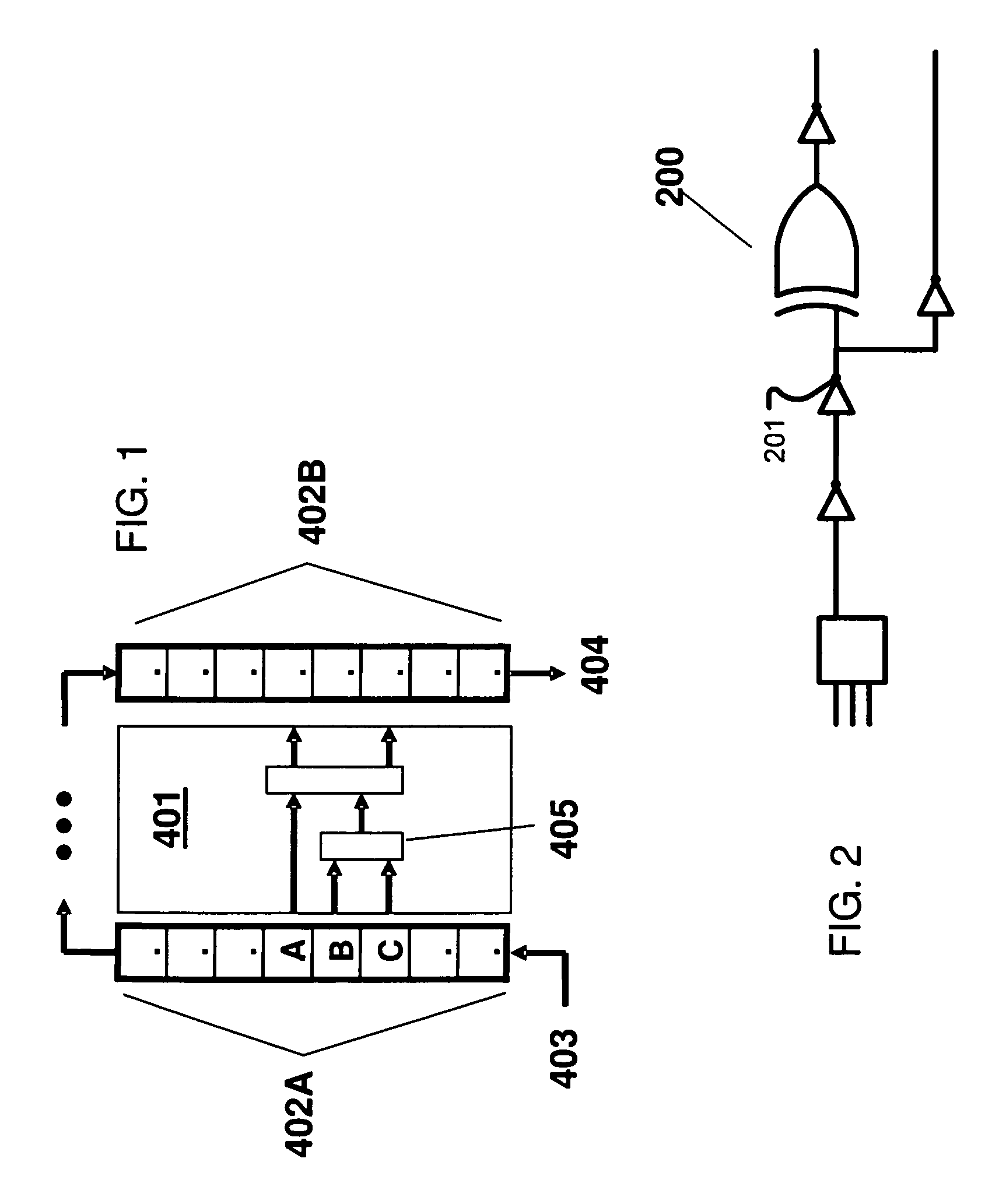

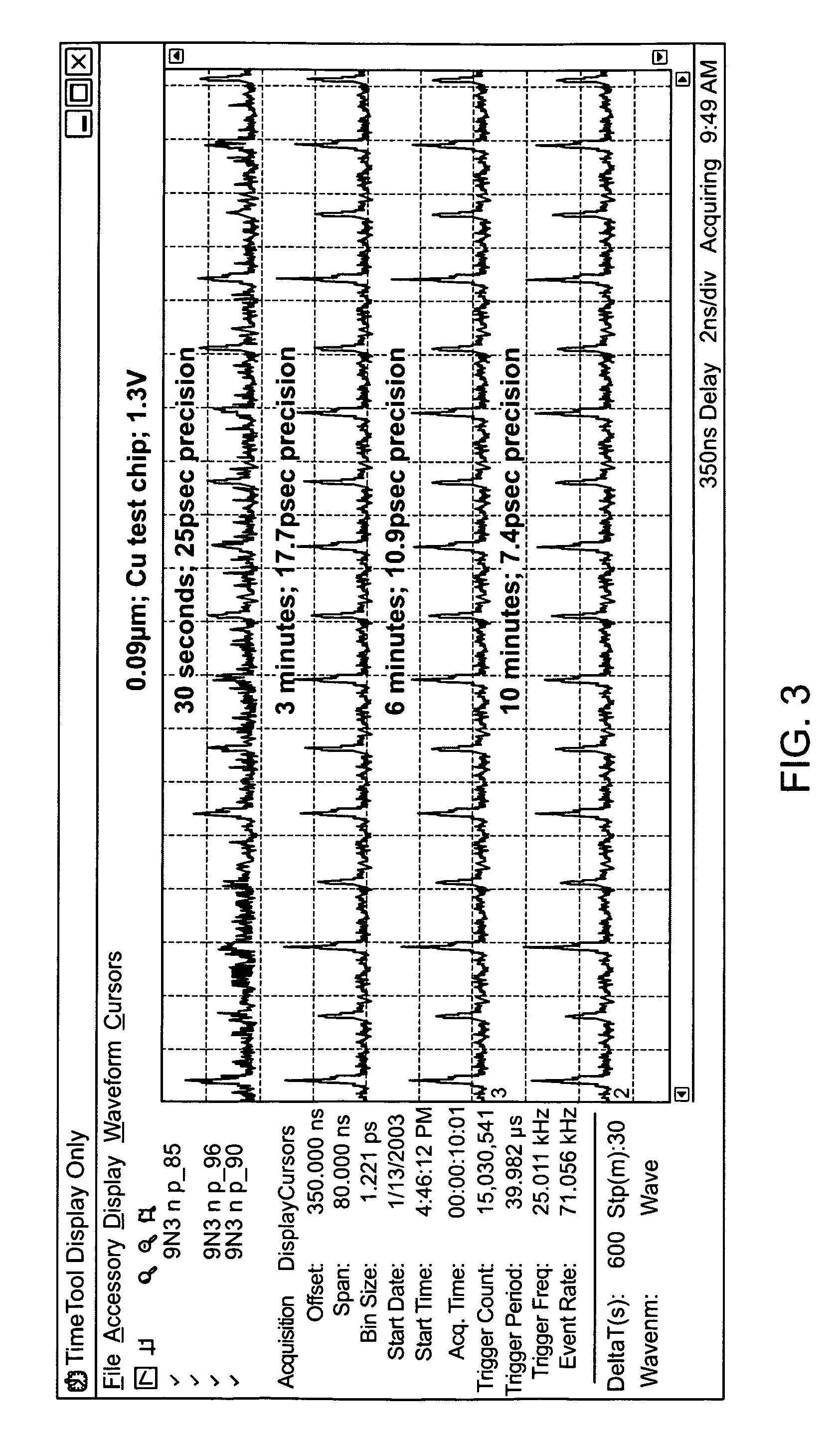

[0034]In the following description, reference is made to the accompanying drawings which illustrate several embodiments of the present invention. It is understood that other embodiments may be utilized and mechanical, compositional, structural, electrical, and operational changes may be made without departing from the spirit and scope of the present disclosure. The following detailed description is not to be taken in a limiting sense, and the scope of the embodiments of the present invention is defined only by the claims of the issued patent.

[0035]Some portions of the detailed description that follows are presented in terms of procedures, steps, logic blocks, processing, and other symbolic representations of operations on data bits that can be performed on computer memory. A proce...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More