Semiconductor chip buried base plate 3D construction and its manufacturing method

A manufacturing method and semiconductor technology, which are applied in the fields of semiconductor/solid-state device manufacturing, semiconductor devices, and semiconductor/solid-state device components, etc., can solve problems such as unstable quality of the overall assembly structure, difficulty in filling insulating materials, and generation of popcorn. , to achieve good quality and product reliability, improve the rate of good, and increase the effect of output

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

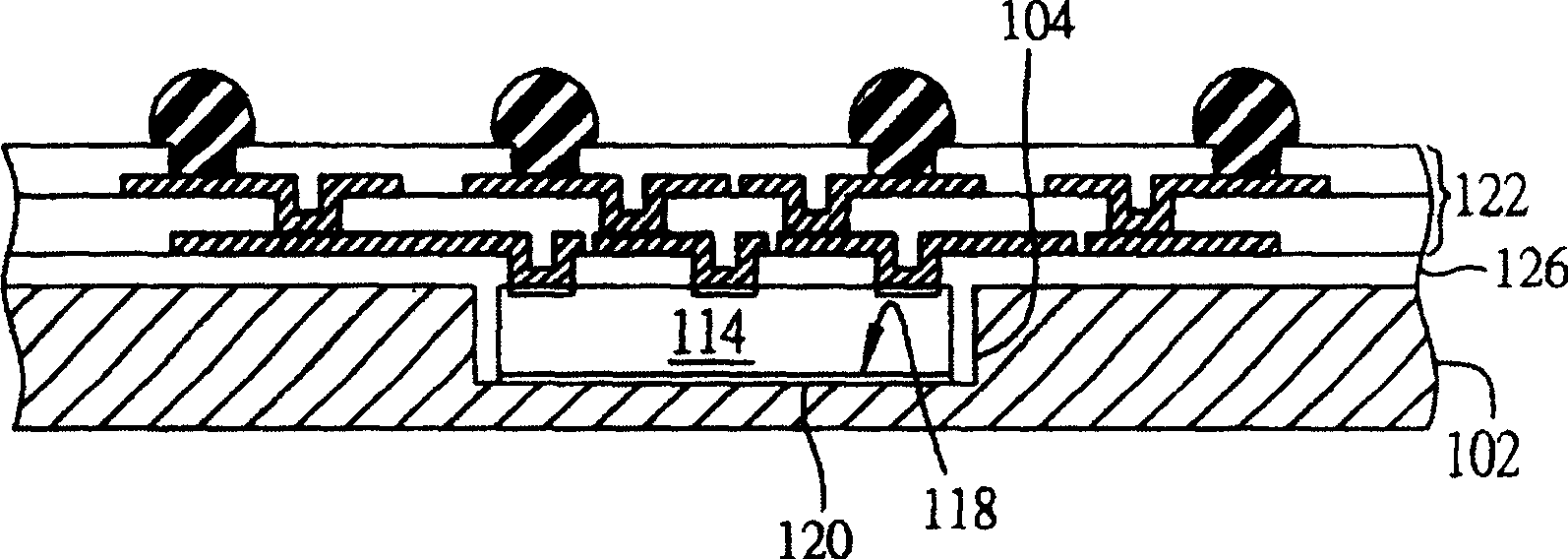

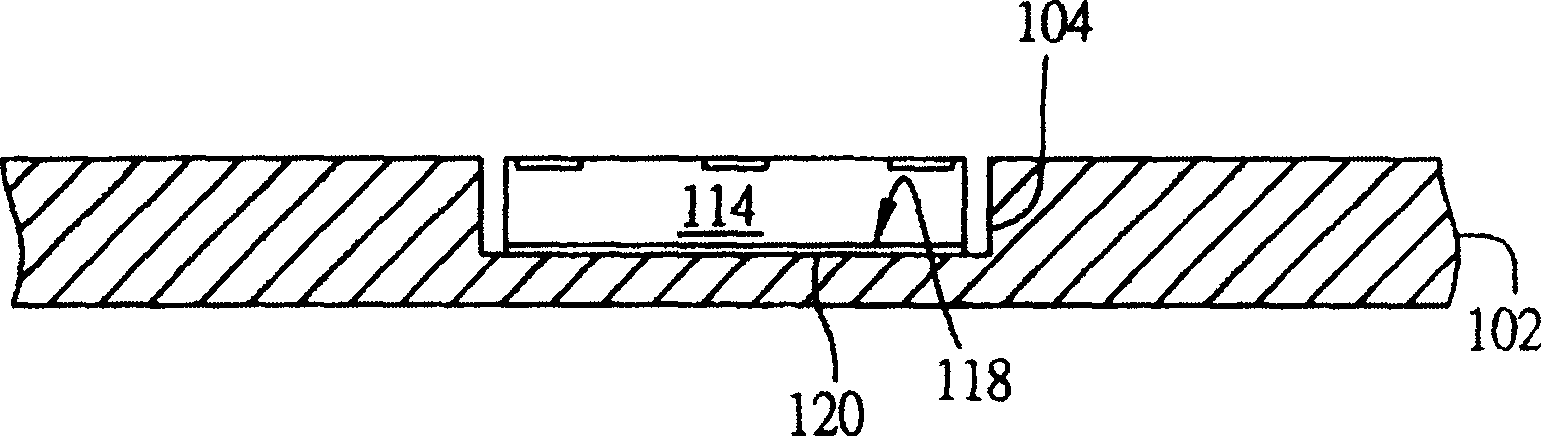

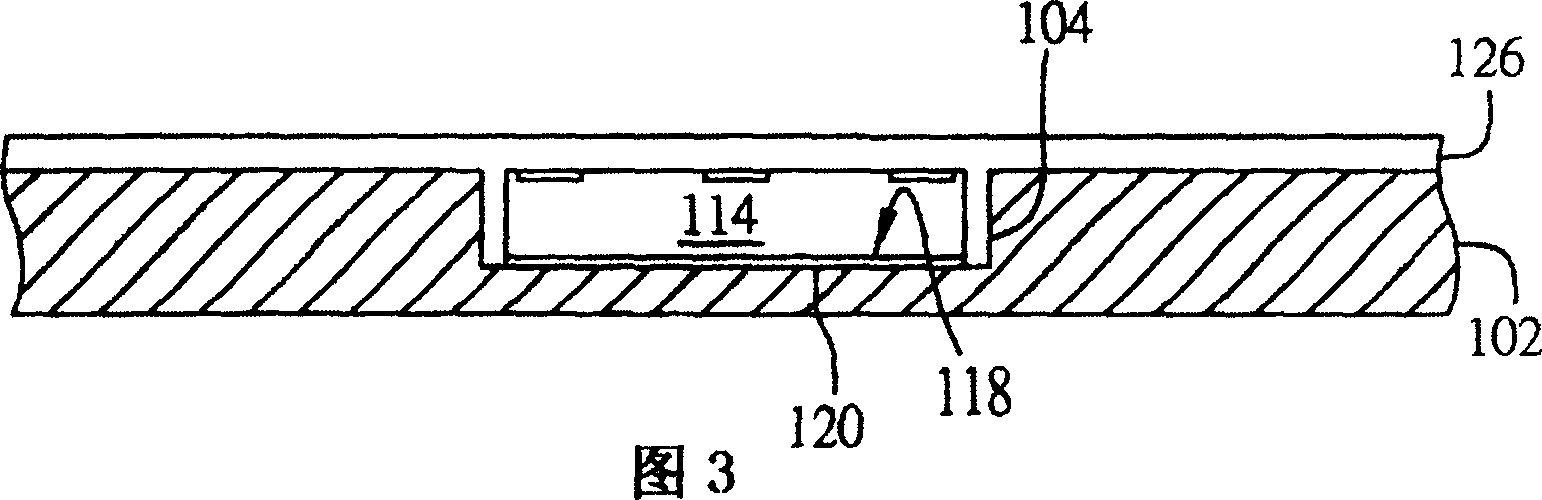

[0026] see Figure 4A , first provide the carrier 400 having the through hole 400a. The carrier 400 can be an insulating core board, a metal plate or a circuit board with circuits, and the thickness of the carrier 400 can be determined as required.

[0027] see Figure 4B , and then bonding the carrier 400 on the first insulating layer 401 . The first insulating layer 401 can be prepreg or film material, such as epoxy resin, polyimide, LCP, bismaleimide / Triple nitrogen trap (BT, Bismaleimide triazine), ABF (Ajinomoto Build-up Film), polyphenylene ether (PPE), polytetrafluoroethylene (PTFE), benzocyclobutene (BCB, benzocylobutene), etc.

[0028] see Figure 4CA non-circuit surface 430 of a semiconductor chip 43 is placed on the first insulating layer 401 by means of a thermally conductive adhesive layer 42 and accommodated in the opening 400 a of the carrier 400 . The chip 43 has a plurality of electrode pads 431 a on the circuit surface 431 .

[0029] see Figure 4D , ...

Embodiment 2

[0034] see Figures 5A to 5H , which are schematic cross-sectional views of Embodiment 2 of the manufacturing method of the semiconductor package structure of the present invention. Embodiment 2 of the semiconductor package structure and its manufacturing method of the present invention is similar to Embodiment 1, the main difference is that a heat dissipation blind hole connecting the non-circuit surface of the semiconductor chip is formed in the first insulating layer, and the heat dissipation blind hole is filled with heat dissipation material And connected to the heat conduction circuit layer in the circuit structure, and then connected to the outside, or can further provide direct external connection with other heat dissipation devices to improve the heat dissipation effect of the semiconductor package structure.

[0035] see Figure 5A , first provide a carrier 500 having a through hole 500a. The carrier 500 can be an insulating core board, a metal plate or a circuit b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More