Making method of the pixel structure and pixel structure

A manufacturing method and technology of pixel structure, applied in semiconductor/solid-state device manufacturing, optics, instruments, etc., can solve the problems of high total production cost, low production qualification rate, long production time, etc., to reduce photocurrent and improve production. Qualification rate, effect of improving characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

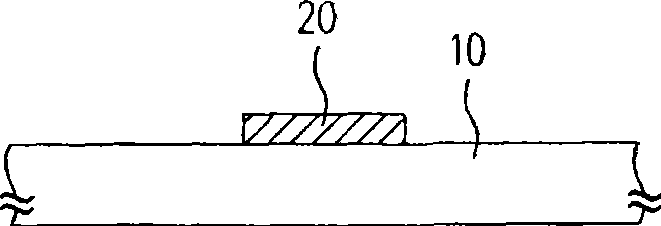

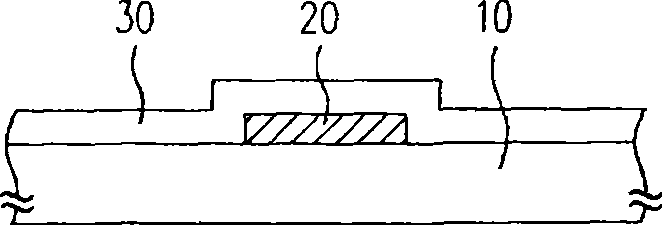

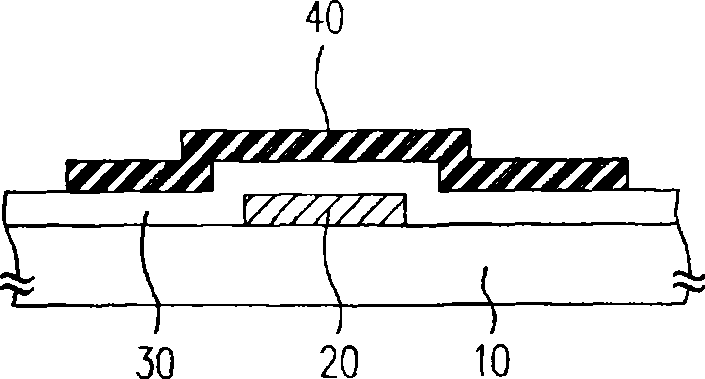

[0072] Figure 2A ~ Figure 2I It is the manufacturing method of the pixel structure of the first embodiment of the present invention.

[0073] Please refer to Figure 2A , first provide a substrate 210 having a pixel region P. Next, a first metal layer 220, a gate insulating layer 230, and a semiconductor layer 240 are sequentially formed on the substrate 210, wherein the material of the semiconductor layer 240 is, for example, amorphous silicon or polysilicon, and the method of forming the first metal layer 220 is, for example, sputtering. (sputtering) or evaporation (evaporation). The material of the gate insulating layer 230 is, for example, silicon oxide or silicon nitride or a laminate thereof, and the method of forming the gate insulating layer 230 is, for example, chemical vapor deposition (CVD). Then, if Figure 2A As shown, the first metal layer 220, the gate insulating layer 230, and the semiconductor layer 240 are patterned through the first half-tone or gray-to...

no. 2 example

[0087] Figure 3A ~ Figure 3I It is the manufacturing method of the pixel structure of the second embodiment. The fabrication method of the pixel structure 300 of this embodiment is similar to that of the first embodiment. In this embodiment, the formation of the transistor pattern 250, the lower capacitor pattern 260 and the lower circuit pattern 270 as well as the fabrication of the patterned dielectric layer 280 and the electrode layer 290 way, such as Figure 3A-3D shown, which is consistent with the first embodiment Figure 2A-2D similar and will not be repeated here.

[0088] Also, please refer to Figure 3E In this embodiment, after patterning the dielectric layer 280 and the electrode layer 290, a doped semiconductor layer 240' is formed on the electrode layer 290, and the doped semiconductor layer 240' is connected to the lower circuit pattern 270, the lower capacitor pattern 260 and The source 250a / drain 250b region of the transistor pattern 250 . The doped semi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More