Three-dimensional multiprocessor system chip

A multi-processor system and processor technology, applied in the direction of electrical digital data processing, instruments, semiconductor devices, etc., can solve the problems of increased chip area consumption, intensified bus resource competition, complex network protocols, etc., to reduce signal delay time, The effect of shortening the length of interconnection lines and improving product yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

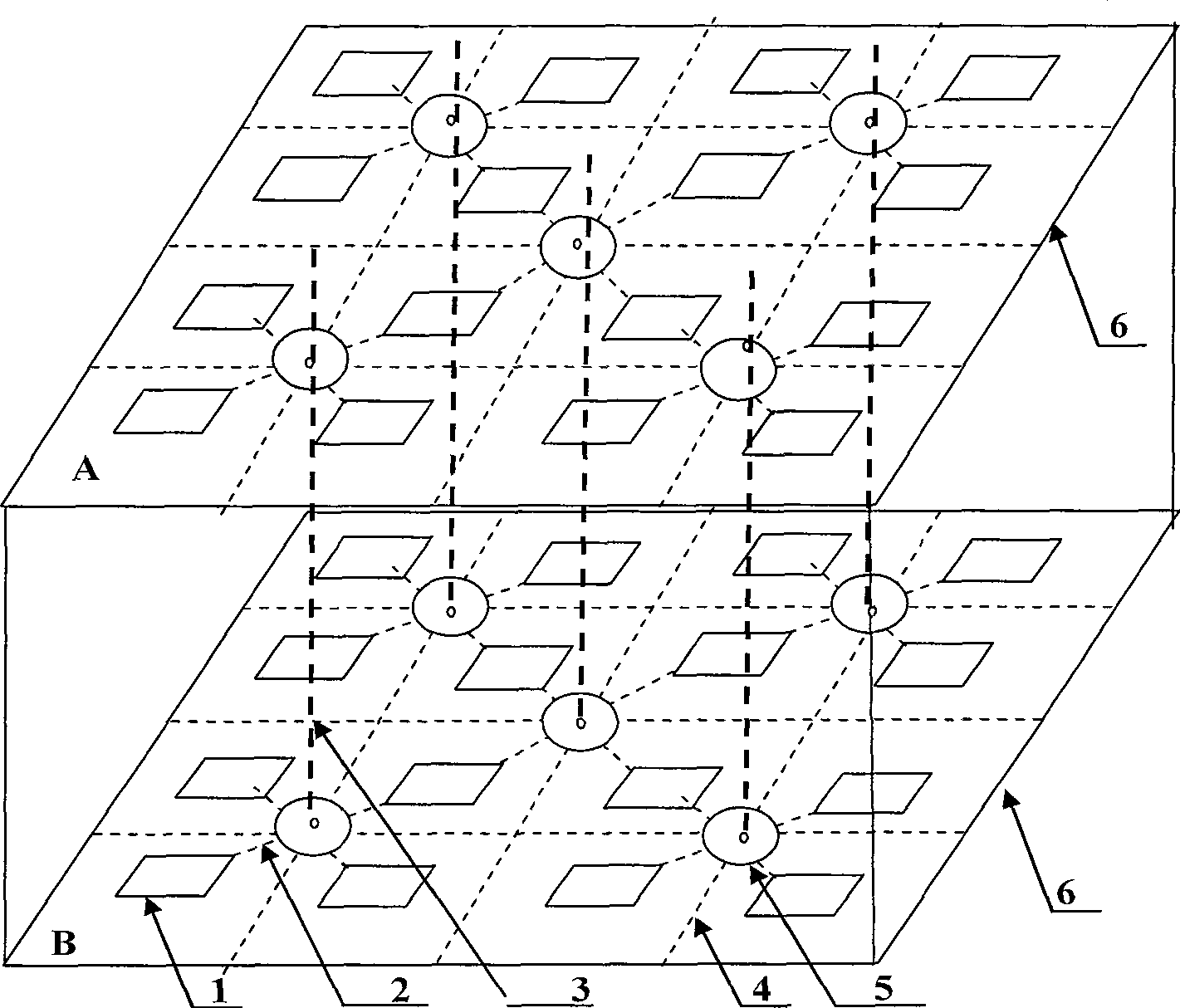

[0033] Examples of the present invention figure 1 -2, it is formed by stacking two VLSI chip wafers 6, 16 processors and 4 three-dimensional on-chip network routers 5 are integrated on the VLSI chip wafer 6, between the processors The three-dimensional network-on-chip routers 5 are connected to each other. The three-dimensional network-on-chip routers 5 between each layer of wafers 6 are connected by vertical data channels.

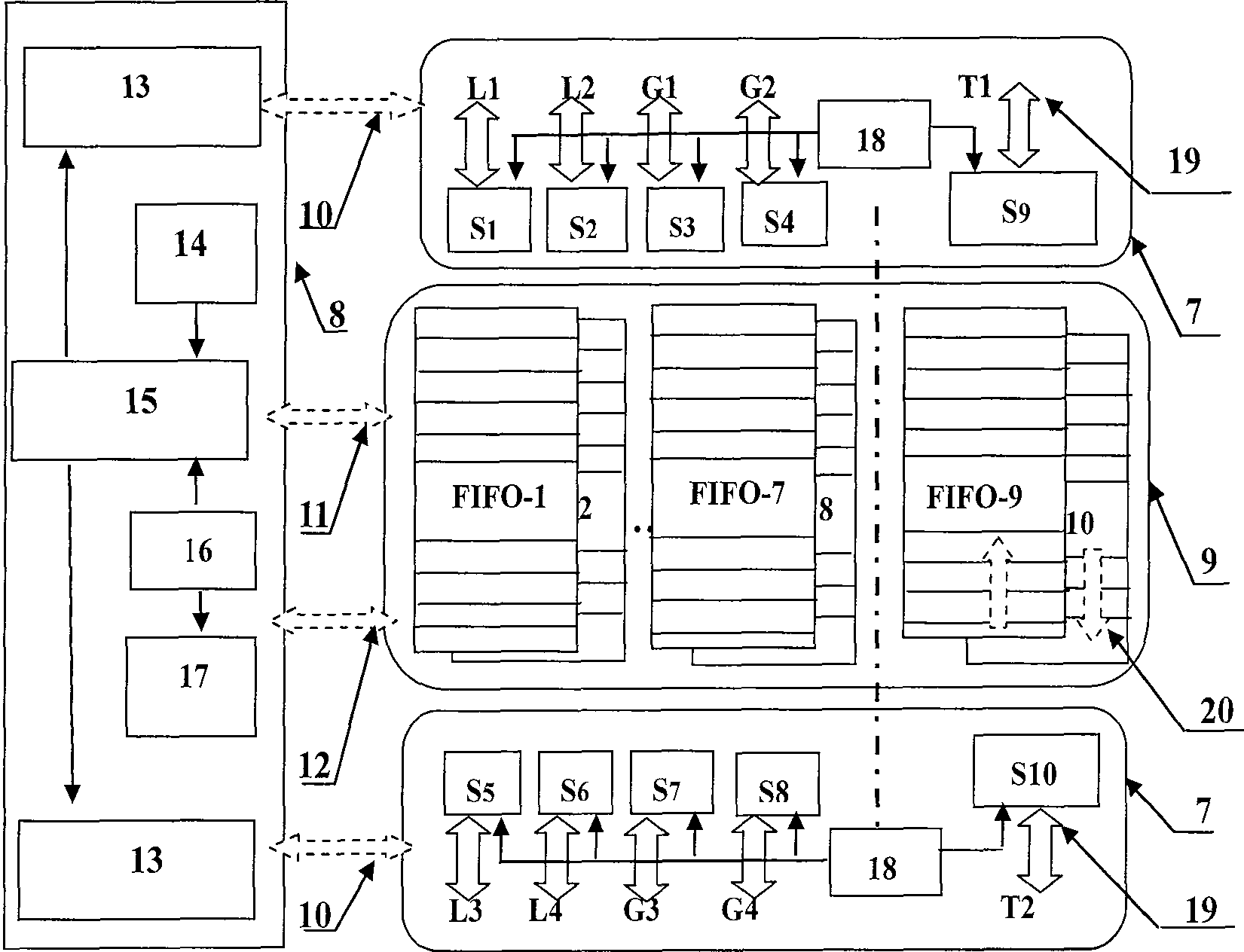

[0034]The three-dimensional on-chip network router 5 is composed of an advanced first-in-first-wave shift buffer memory, a synchronous matrix switch array, a digital routing decision module 8, and a parallel network interface; the parallel network interface input port is connected to the synchronous matrix switch array; The output interface of the synchronous matrix switch array on one side of the memory is connected to the input interface of the first-in-first-line wave shift buffer memory, and the output interface of the advanced first-line wave shift b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More