Method of fabrication SiGe heterojuction bipolar transistor

A device manufacturing method and transistor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of low parasitic capacitance and small transistor size, and achieve the effect of simple isolation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

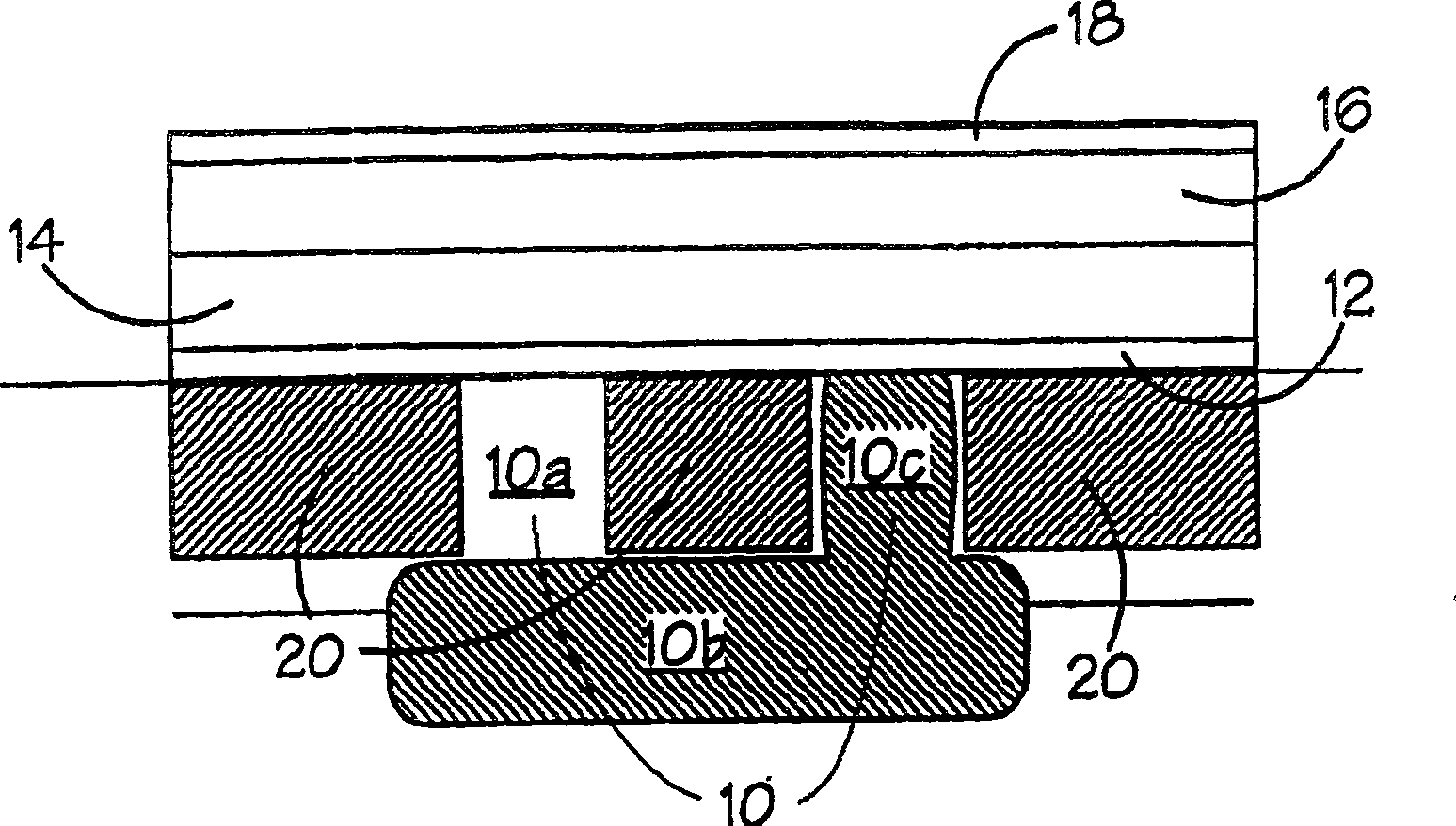

[0021] figure 1 The initial structure is shown, which comprises a standard BiCMOS p-doped substrate 10, represented by a buried collector contact 10b, an N-type collector epitaxial layer 10a, and a surface to provide a buried n-layer collector contact. The contacts between 10b and n plug the dimples 10c. Finally field isolation regions are provided in the form of two shallow trench isolation regions 20 . A thermal oxide layer 12 is grown on top of the substrate 10, followed by a layer stack consisting of a boron in situ doped polysilicon deposition layer 14, a TEOS layer 16, and an amorphous silicon layer 18.

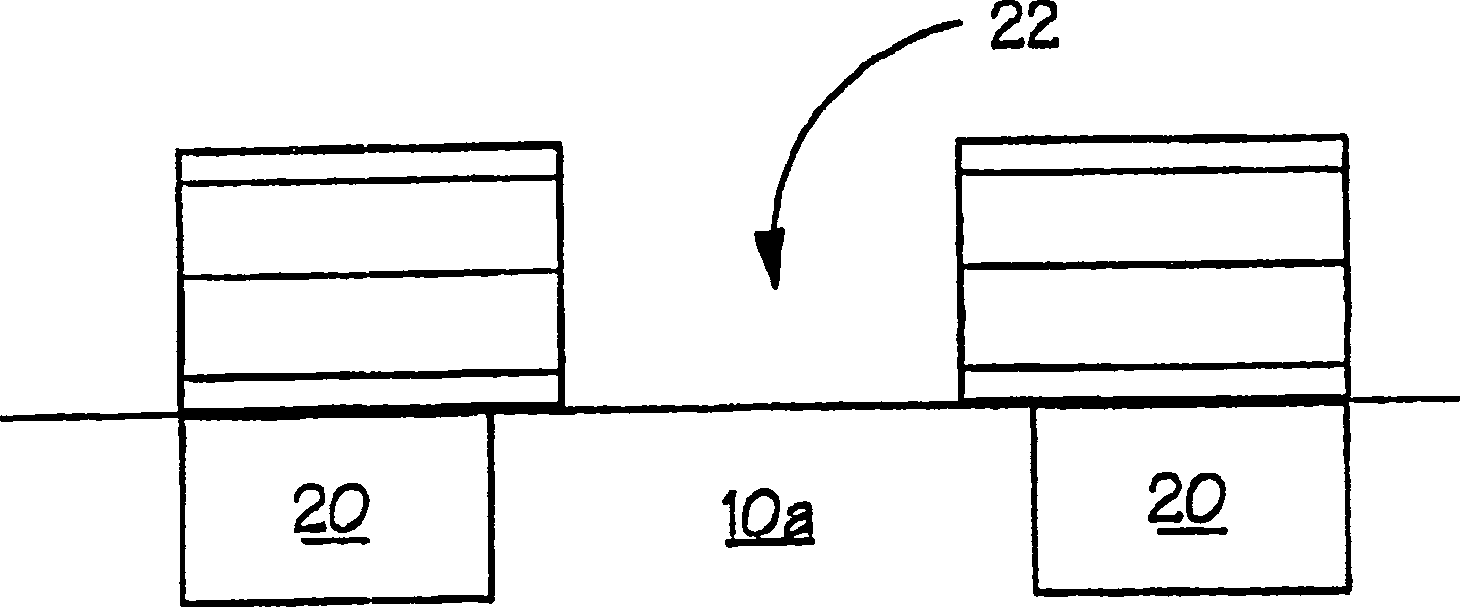

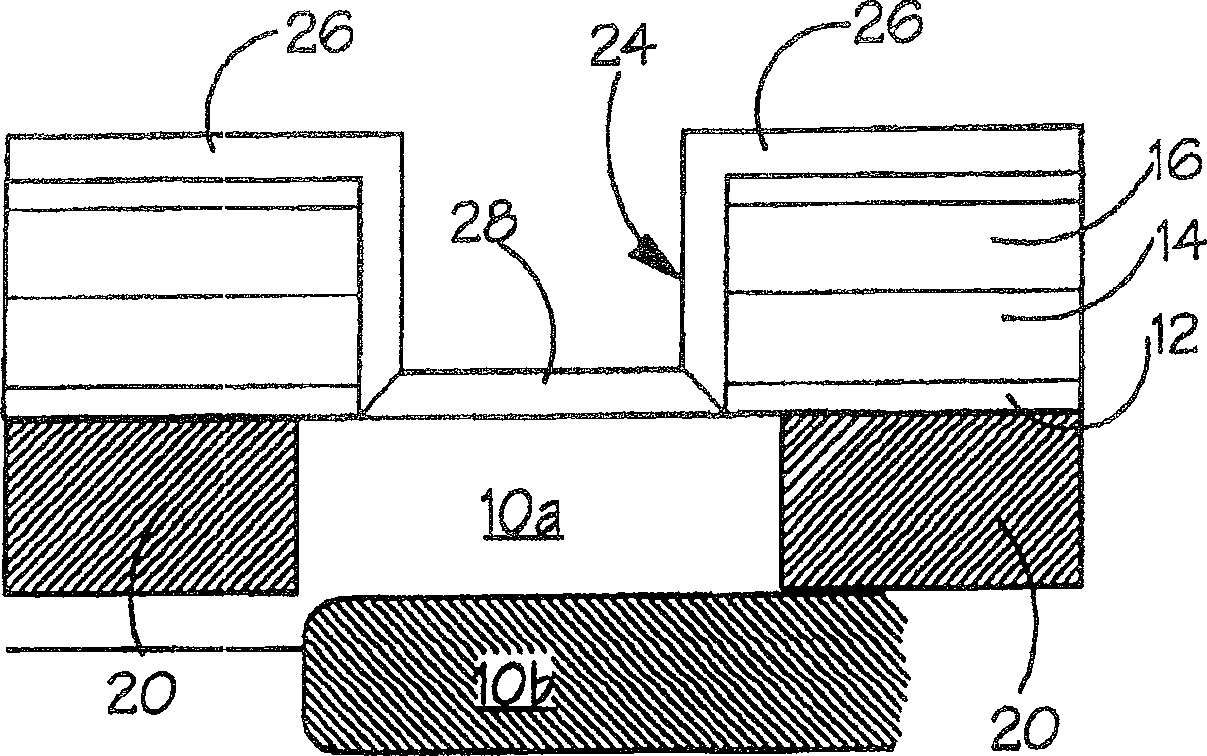

[0022] Refer below figure 2 , which is an enlarged detail of the active region, the transistor region 22 is opened by etching a well through the entire layered stack formed on the thermal oxide layer 12. This is accomplished using a plasma etch step to etch through the amorphous silicon layer 18, the TEOS layer 16, and the polysilicon layer 14. Thermal oxide 12 se...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com