Method and structure for impriving the measurment accuracy of LDD doping layer square resistance

A technology for sheet resistance and measurement accuracy, which is applied in the direction of semiconductor/solid-state device testing/measurement, circuits, electrical components, etc., can solve the problems of inaccurate measurement results and poor repeatability, and achieve the effect of improving accuracy and accurate sheet resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0069] The first doping ion is indium, the second doping ion is boron, and the second doping layer is a PLDD doping layer.

[0070] Such as figure 2 As shown, a semiconductor substrate 10 is provided, which may be monocrystalline silicon or polycrystalline silicon.

[0071] Cleaning the surface of the semiconductor substrate 10 to remove impurity particles, organic or inorganic pollutants, and a natural oxide layer on the surface of the semiconductor substrate 10 .

[0072] Optionally, a thin oxide layer (not shown) can be formed on the surface of the semiconductor substrate 10, which can protect the surface of the semiconductor substrate 10 from contamination and prevent subsequent ion implantation from damaging the semiconductor substrate. The excessive damage of 10 can also be used as an oxidation buffer layer to control the depth of ion implantation.

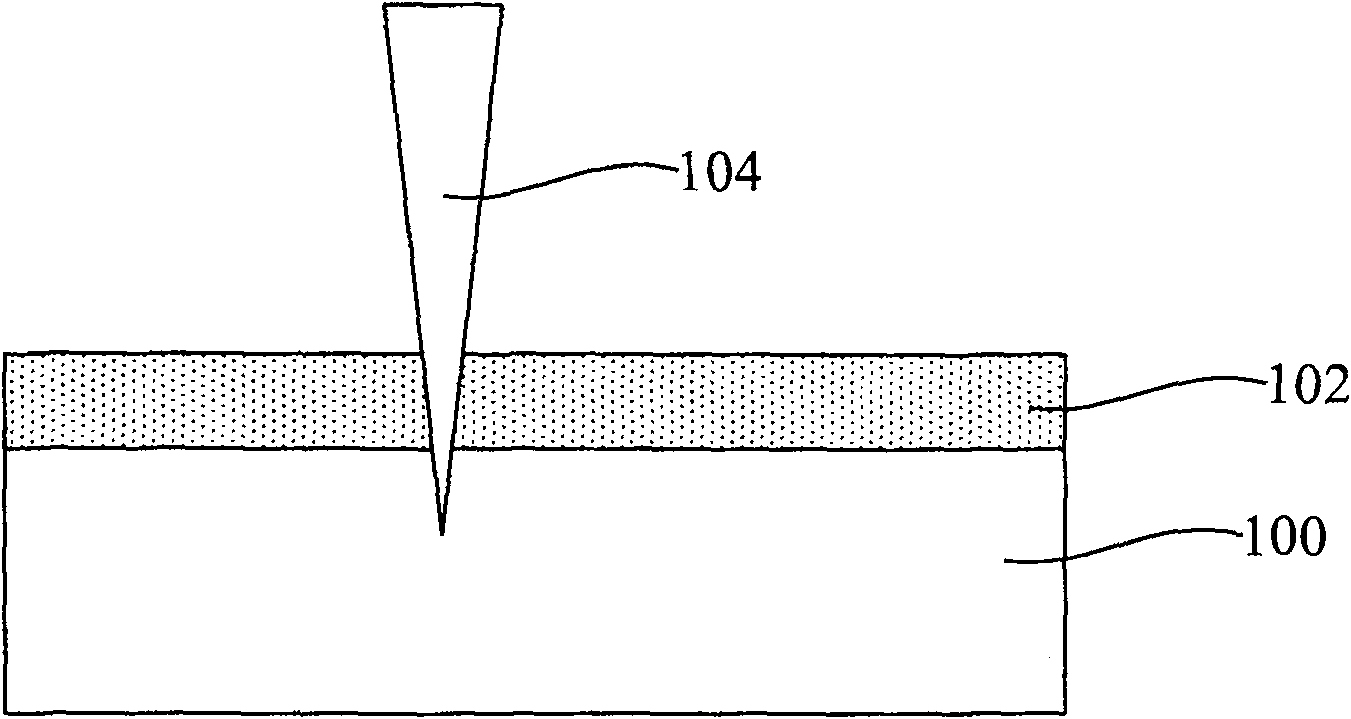

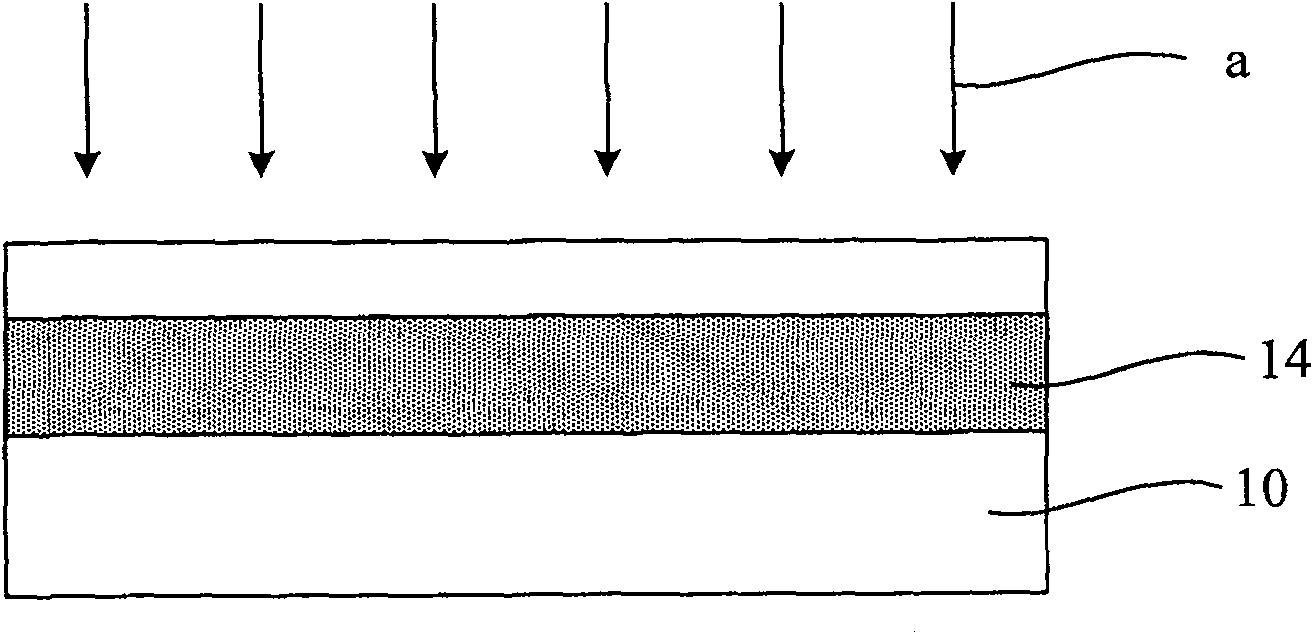

[0073] Next, a surface pre-amorphous implantation (Pre-Amorphous Implantation, PAI) is performed on the semiconductor s...

Embodiment 2

[0088] The first doping ion is indium, the second doping ion is boron, and the second doping layer is a PLDD doping layer.

[0089] Provide a semiconductor substrate 20, such as Figure 6 As shown in the schematic cross-sectional view, the semiconductor substrate 20 may be single crystal silicon or polycrystalline silicon. Cleaning the surface of the semiconductor substrate 20 to remove impurity particles, organic or inorganic pollutants, and a natural oxide layer on the surface of the semiconductor substrate 20 .

[0090] Perform surface pre-amorphization implantation on the semiconductor substrate 20 to make the surface of the semiconductor substrate 20 in an amorphized state.

[0091] The surface pre-amorphization silicidation implantation generally uses high-mass ions, for example, the impurity implanted in the pre-amorphization implantation can be one of Ge, Si, and Sb.

[0092] By bombarding the surface of the semiconductor substrate 20 with high-mass ions, the surface...

Embodiment 3

[0103] The first doping ion is indium, the second doping ion is boron, and the second doping layer is a PLDD doping layer.

[0104] Provide a semiconductor substrate 30, such as Figure 7 As shown, the semiconductor substrate 30 may be single crystal silicon or polycrystalline silicon. Cleaning the surface of the semiconductor substrate 30 to remove impurity particles, organic or inorganic pollutants, and a natural oxide layer on the surface of the semiconductor substrate 30 .

[0105] A first doping ion implantation is performed on the semiconductor substrate 30 to form a first doping layer 34 in the semiconductor substrate 30 .

[0106] The first dopant ion is indium, the implanted energy may be 30 to 200KeV, and the dose may be 5×10 12 up to 5×10 13 atom / cm 2 , the inclination angle during injection can be 0 degrees.

[0107] The energy of the first dopant ion implantation is relatively high, and the implantation depth is relatively deep, which is greater than the impl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More