Wafer-level encapsulation and cutting method

A technology of wafer-level packaging and cutting method, which is applied in the manufacturing of electrical components, electric solid-state devices, semiconductor/solid-state devices, etc., and can solve the problems of structural damage, decline in yield, and large package die size.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

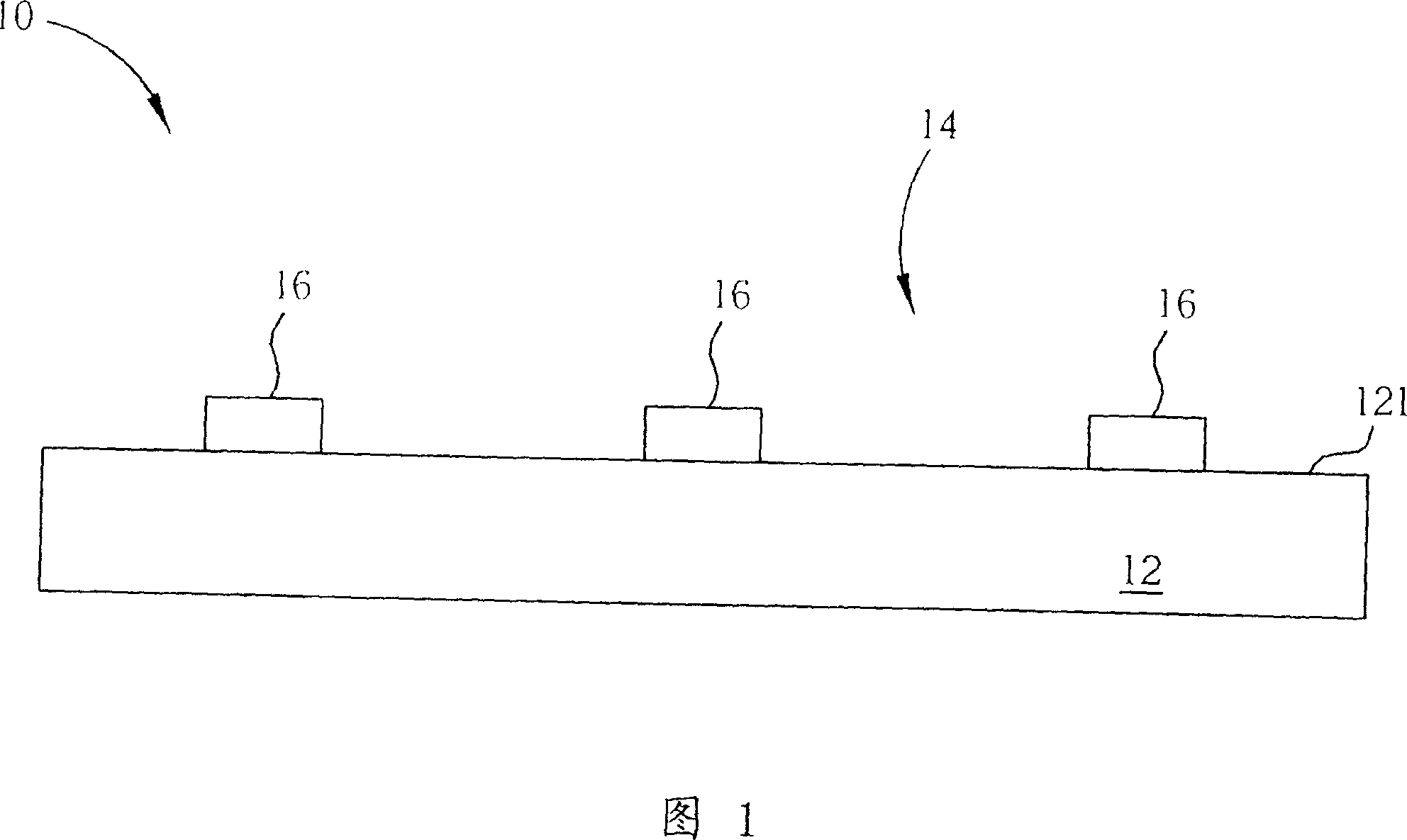

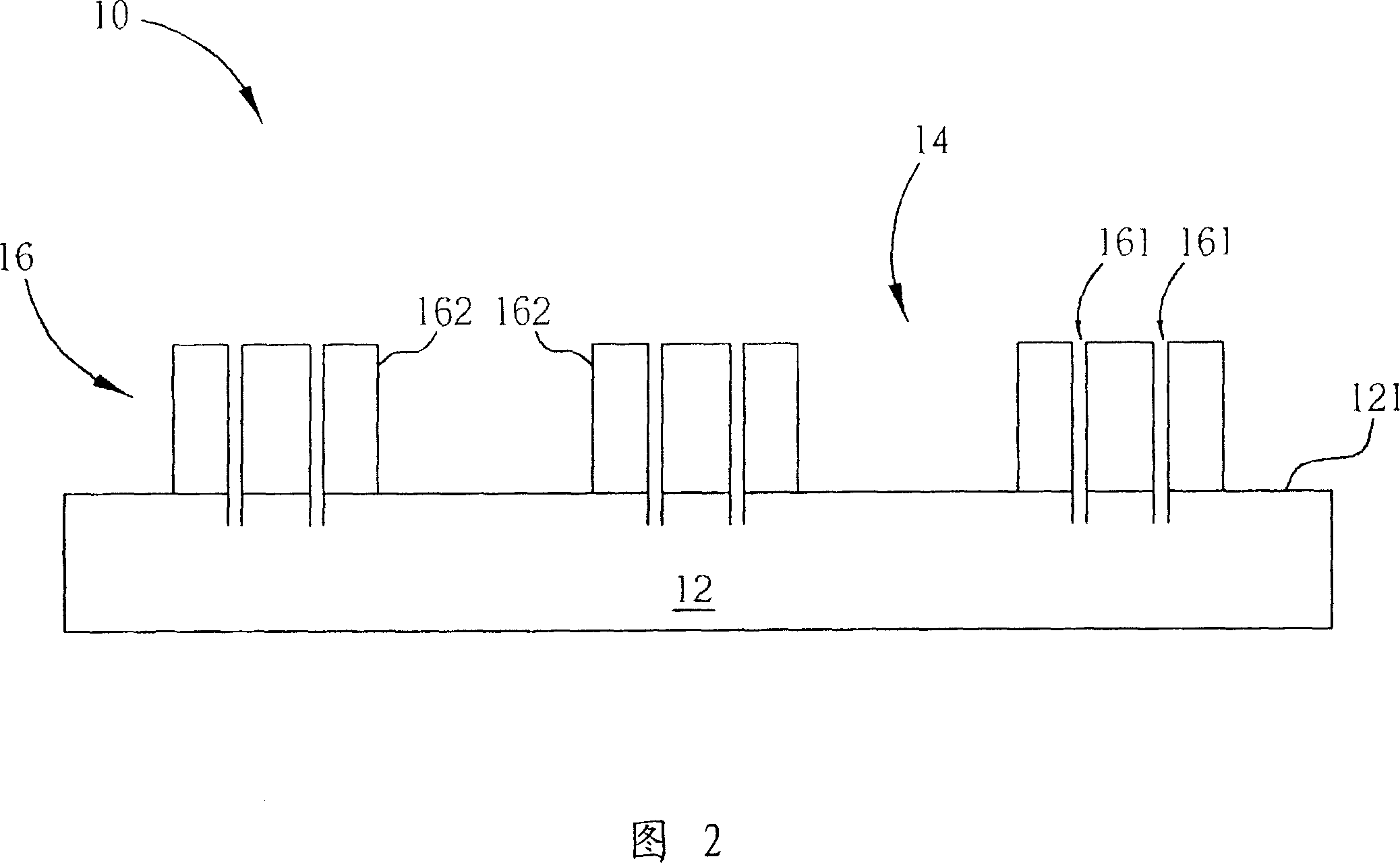

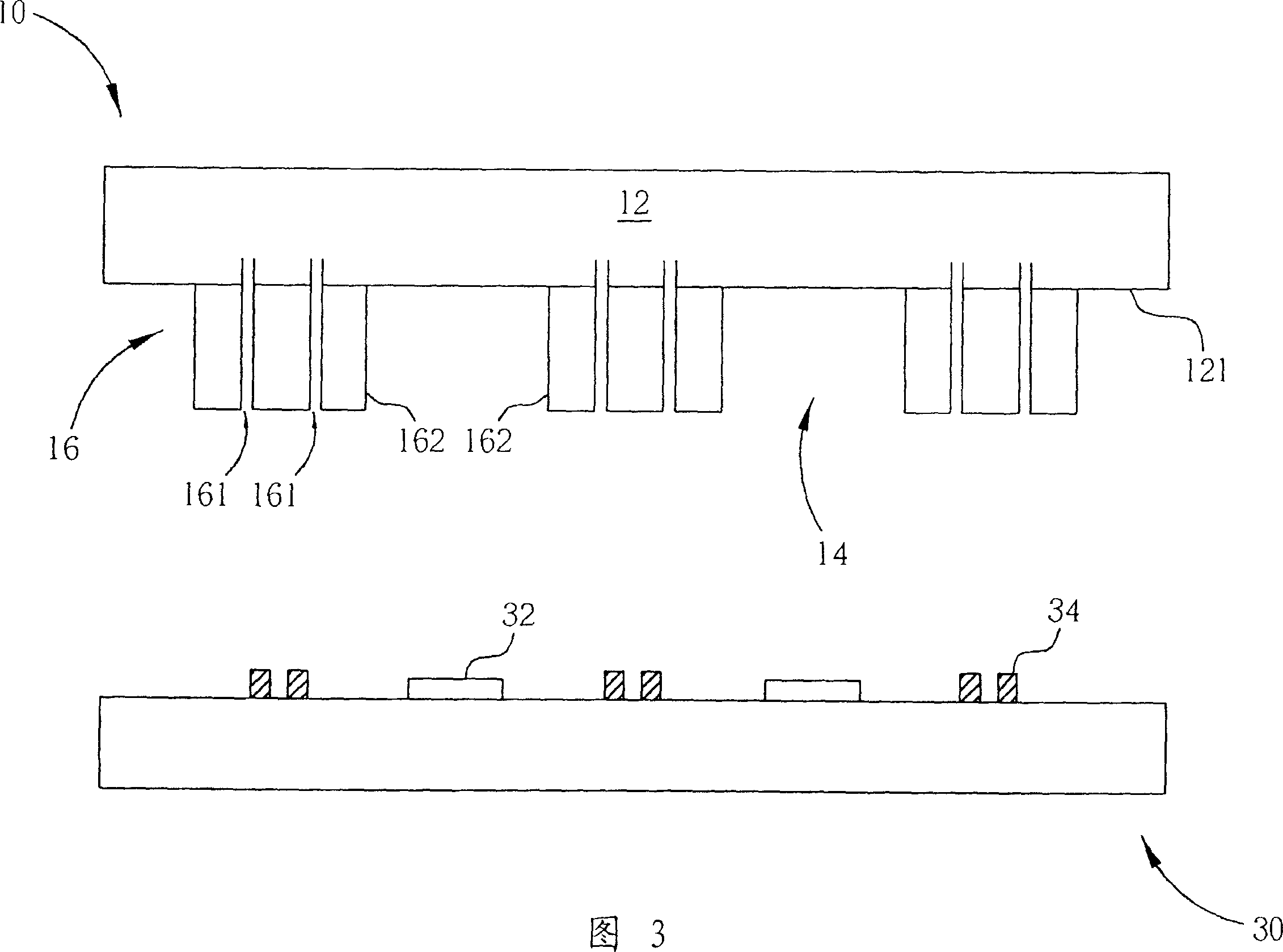

[0018] 1 to 9 are schematic diagrams of a wafer-level packaging cutting method according to a preferred embodiment of the present invention. As shown in FIG. 1, FIG. 1 is a packaging chip 10 used as an upper cover structure. The packaging chip 10 includes a transparent substrate 12, a wafer pattern 16 and a plurality of concave cavities 14 defined by the wafer pattern 16, and the cavity 14 is located on the front side 121 of the packaging chip 10 . The transparent substrate 12 is made of quartz, plastic or glass or other transparent materials, and in this embodiment, the transparent substrate 12 is a glass substrate. Referring to FIG. 2 , the packaged wafer 10 is subjected to a pre-cutting process according to a predetermined position, wherein the pre-cutting process can be wet wafer dicing, such as a wet etching process, or dry wafer dicing, such as a dry etching process or using a dicing tool. The above-mentioned pre-cutting process forms a plurality of grooves 161 on the w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More