Silicon lining bottom plane LED integrated chip and producing method

A technology of integrated chip and silicon substrate, which is applied in the field of silicon substrate planar LED integrated chip and its manufacturing, can solve the problems of easy short circuit of integrated chip and inability to realize series connection, etc., and achieve reduction of operation time of bonding process, low cost, The effect of occupying a small area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

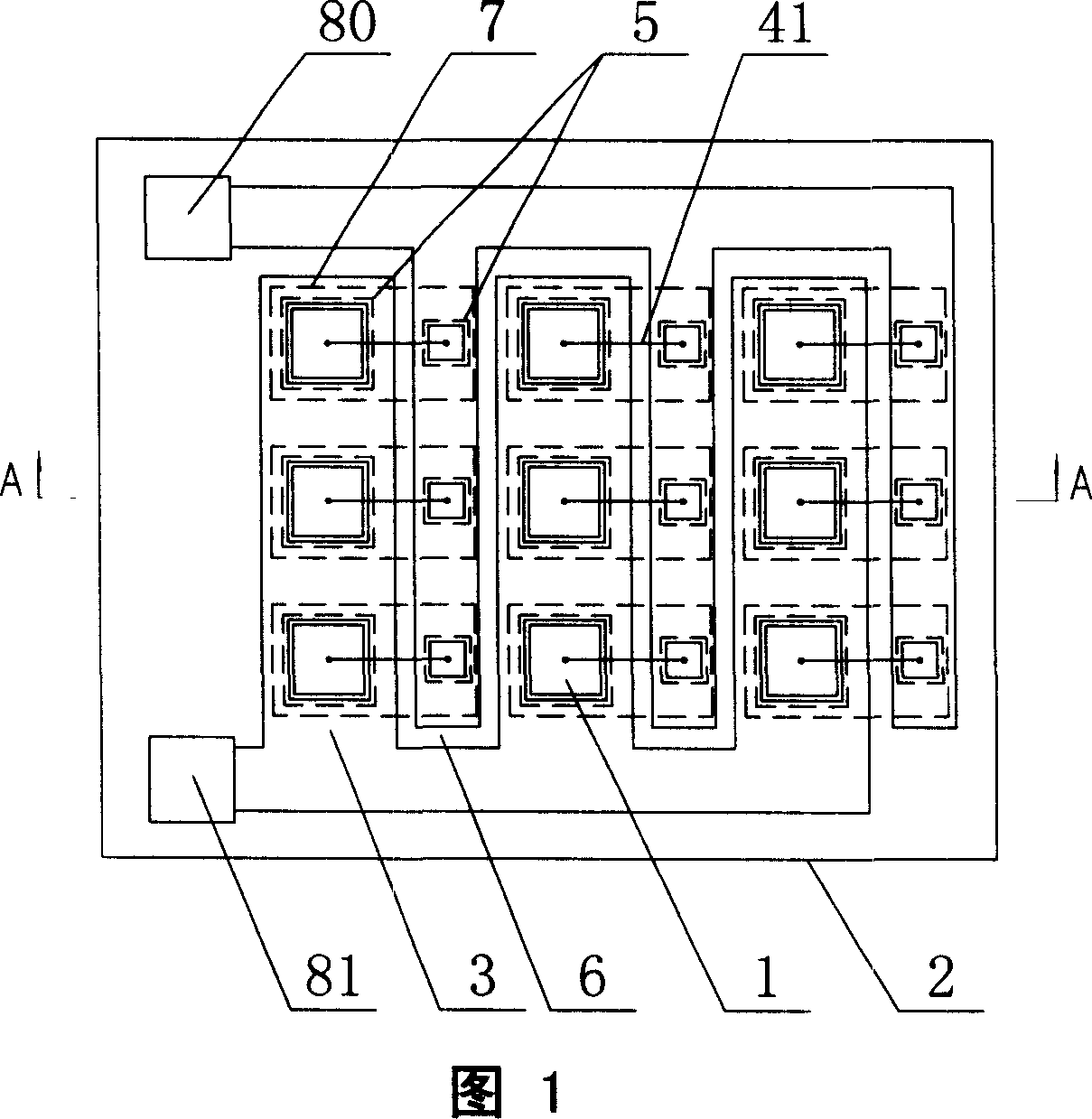

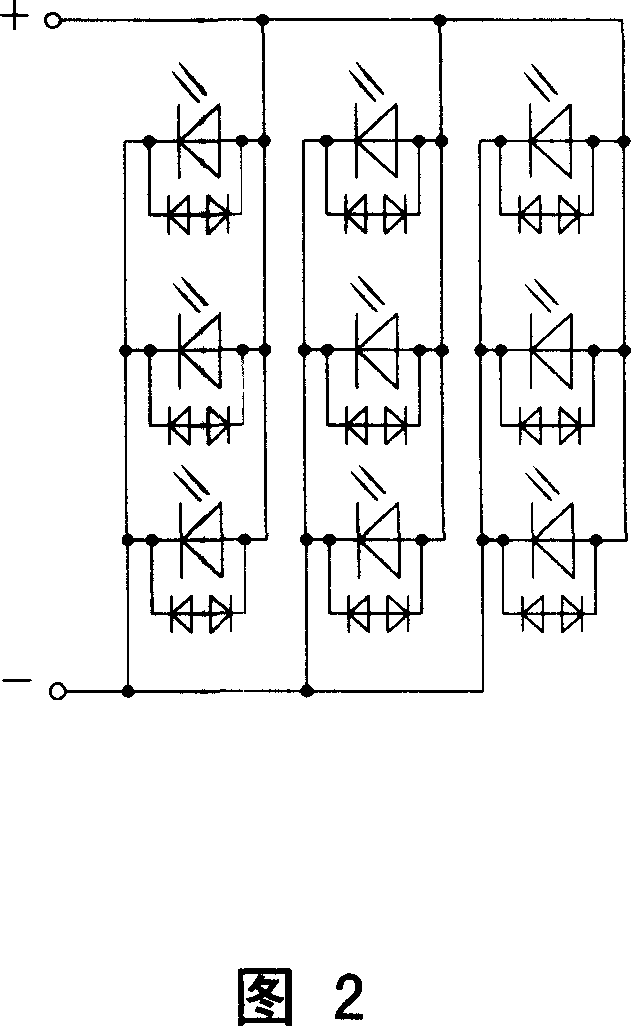

[0053] As shown in Fig. 1, Fig. 2, and Fig. 13, the silicon substrate planar LED integrated chip of this embodiment is a formally mounted LED integrated chip, which includes nine LED bare chips 1 and a silicon substrate 2, and the LED bare chip 1 includes Gallium arsenide (GaAs) substrate 10 and N-type epitaxial layer 11, P-type epitaxial layer 12, of course, the substrate 10 can also be a silicon carbide (SiC) substrate, that is, the LED bare chip 1 is a single electrode Chip, the silicon substrate 2 is an N-type silicon substrate, and the top surface of the silicon substrate 2 has two separate deposited metal layers 3 at each of the LED bare chips 1, and the LED bare chips 1 are mounted Welded on each of the metal layers 3, that is, the substrate 10 is directly welded on the metal layer 3, and the P-type epitaxial layer 12 is correspondingly welded on an adjacent metal layer 3 through a metal wire 41 , the silicon substrate 2 has a P-type well region 7 at each of the LED bar...

Embodiment 2

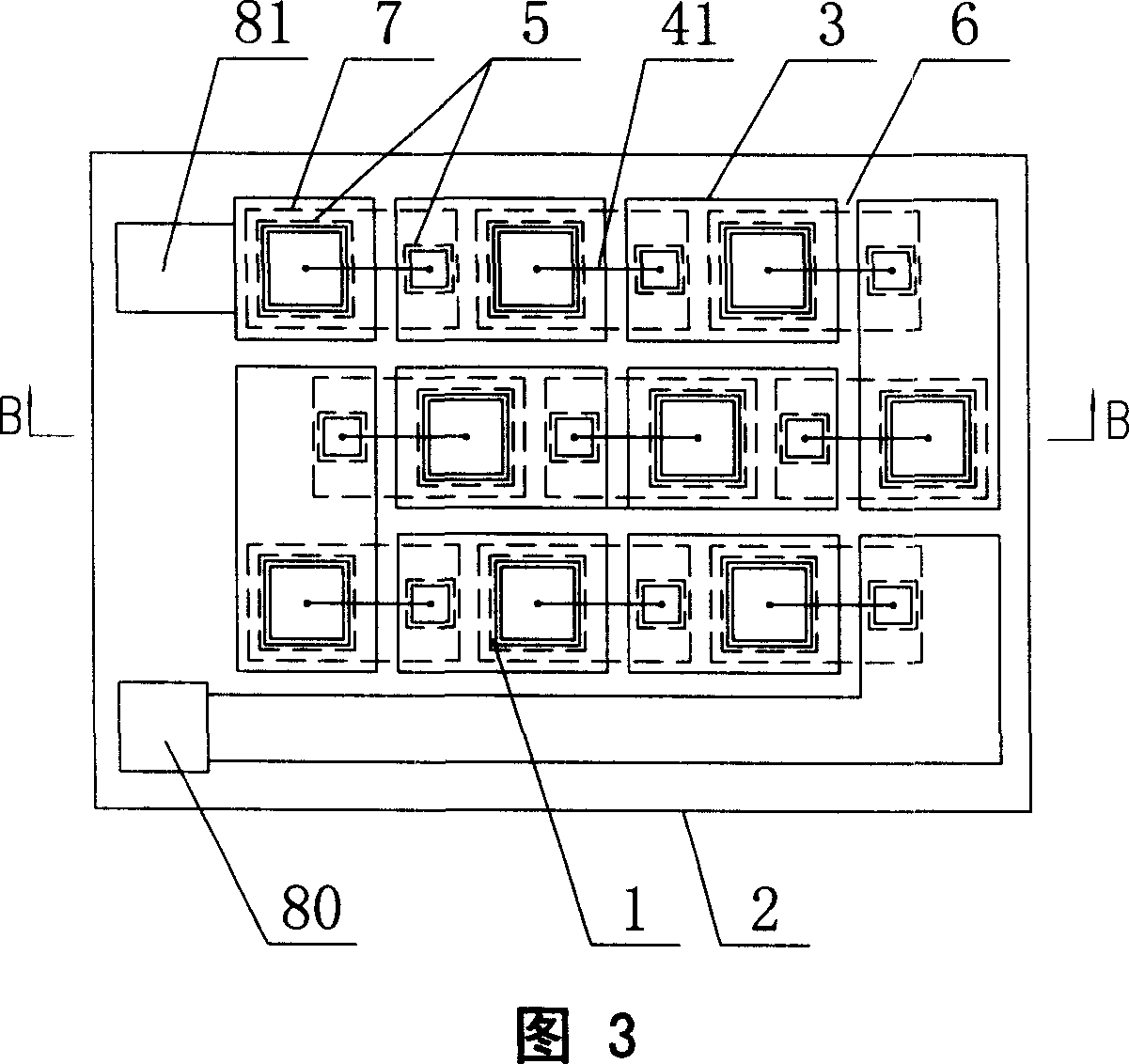

[0062] As shown in Figure 3, Figure 4, and Figure 14, the difference between this embodiment and Embodiment 1 lies in: the connection mode between the LED bare chips 1 through the metal layer 3 - each of the LED chips 1 in this embodiment The LED bare chips 1 are connected in series, that is, all the LED bare chips 1 between the anode contact 80 and the cathode contact 81 are connected in series.

[0063] The remaining features of this embodiment are the same as those of Embodiment 1.

Embodiment 3

[0065] As shown in Fig. 5, Fig. 6, and Fig. 15, the difference between this embodiment and Embodiment 1 lies in: the connection method between each of the LED bare chips 1 through the metal layer 3—— The above-mentioned LED bare chips 1 are connected in series every three to form a group, and then the three groups are connected in parallel.

[0066] The remaining features of this embodiment are the same as those of Embodiment 1.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More