Semiconductor device and its manufacturing method

A manufacturing method and semiconductor technology, which is applied in the direction of semiconductor devices, semiconductor/solid-state device parts, electric solid-state devices, etc., can solve the problems of thicker semiconductor devices, higher costs, and increased thickness of semiconductor devices, so that the manufacturing process will not complicating effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

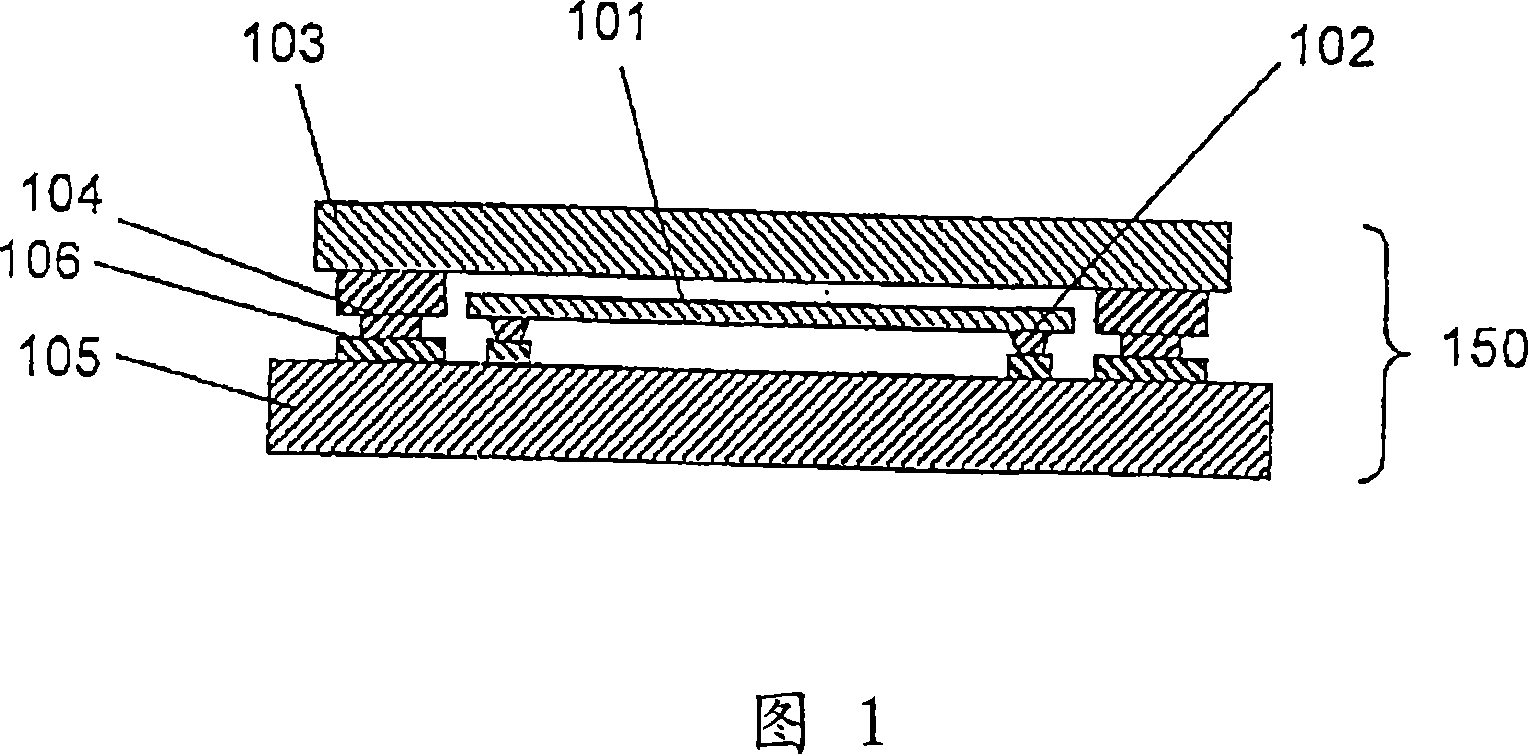

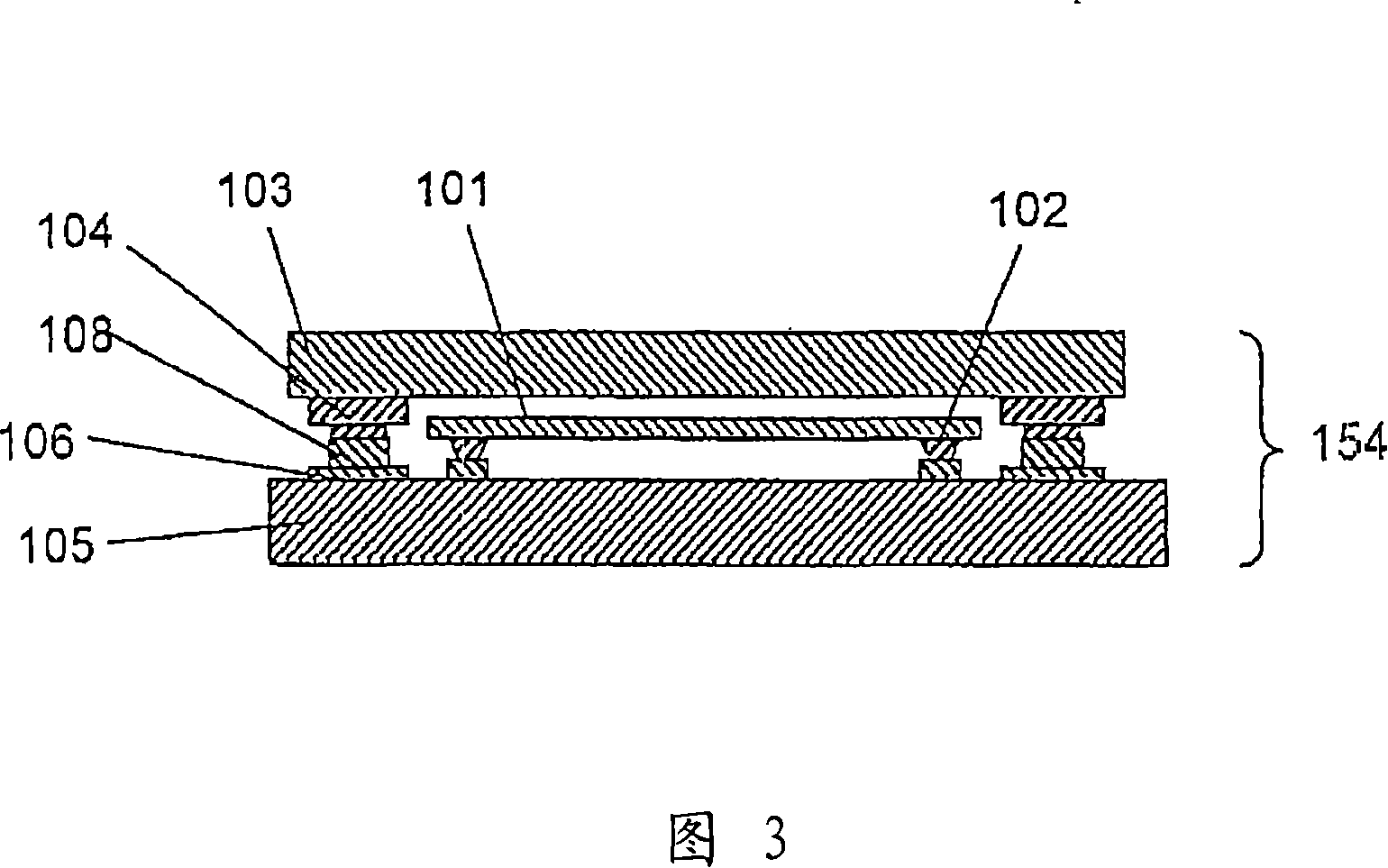

[0092] FIG. 1 is a cross-sectional view of a semiconductor device showing the basic structure of the semiconductor device of the present invention.

[0093] As shown in the figure, the semiconductor device 150 is three-dimensionally mounted with two semiconductor chips 101 and 103 by flip-chip mounting.

[0094] That is, on the first semiconductor chip (lower semiconductor chip) 101, a bump electrode (a low-level electrode: hereinafter referred to as a first electrode) 102 formed by metal plating or the like is formed, and the first electrode 102 It is directly connected to a predetermined wiring pattern 106 formed on the substrate 105 . That is, the first semiconductor device is mounted on the main surface of the substrate 105 by flip-chip mounting.

[0095] Similarly, a tall electrode 104 (hereinafter referred to as a second electrode) is formed on the second semiconductor chip 103 , and the second electrode 104 is directly connected to a predetermined wiring pattern 106 fo...

Embodiment approach 2

[0120] 4 is a cross-sectional view of a semiconductor device showing another example of the semiconductor device of the present invention (an example in which a first semiconductor chip and a second semiconductor chip are integrated). In FIG. 4 , the same reference numerals are assigned to the same parts as those in the illustrations described above, and the description of the common parts will be omitted. This also applies to the illustrations below.

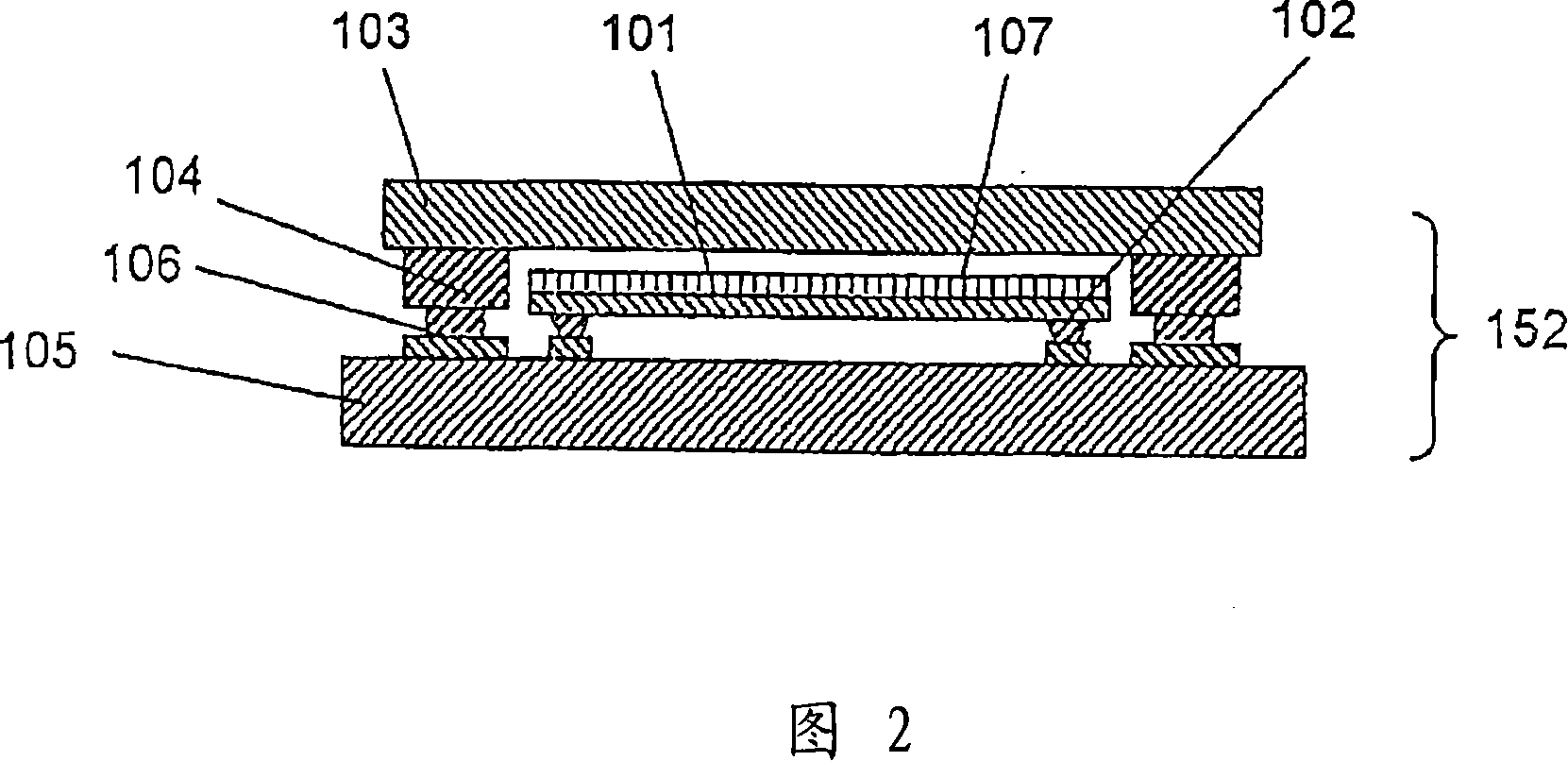

[0121] In the aforementioned embodiments, the two semiconductor chips are flip-chip mounted separately, but in this embodiment, the two semiconductor chips (101, 103) are first bonded, and then flip-chip mounted. The integrated semiconductor chips are mounted on the substrate 105 together.

[0122] That is, in the above-mentioned embodiments, the first semiconductor chip 101 and the second semiconductor chip 103 are not in contact or in a state of not being closely attached, but in this embodiment, the upper surface of the fir...

Embodiment approach 3

[0134] 5 is a cross-sectional view of a semiconductor device showing another example of the semiconductor device of the present invention (an example in which the entire semiconductor device is sealed with resin).

[0135] In the present embodiment, the package structure is formed by sealing the bare chips (101, 103) with resin, thereby improving the water resistance or environment resistance of the semiconductor device. As shown in FIG. 5, a resin sealing body 109 for sealing the entire semiconductor device is provided on a semiconductor device 158 of this embodiment (the other structures are the same as those in FIG. 1).

[0136] The sealing resin 109 is composed of epoxy resin, polyimide resin, acrylic resin, silicone resin, etc. with high heat resistance (glass transition temperature: 120-180°C), and preferably does not contain corrosion-inducing components such as halogen and organic phosphoric acid. . In addition, the curing temperature of the sealing resin 109 is 100 t...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Height | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More