Method for improving silicate nickel layer performance and method for forming PMOS transistor

A nickel silicide layer, transistor technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as spike phenomenon

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

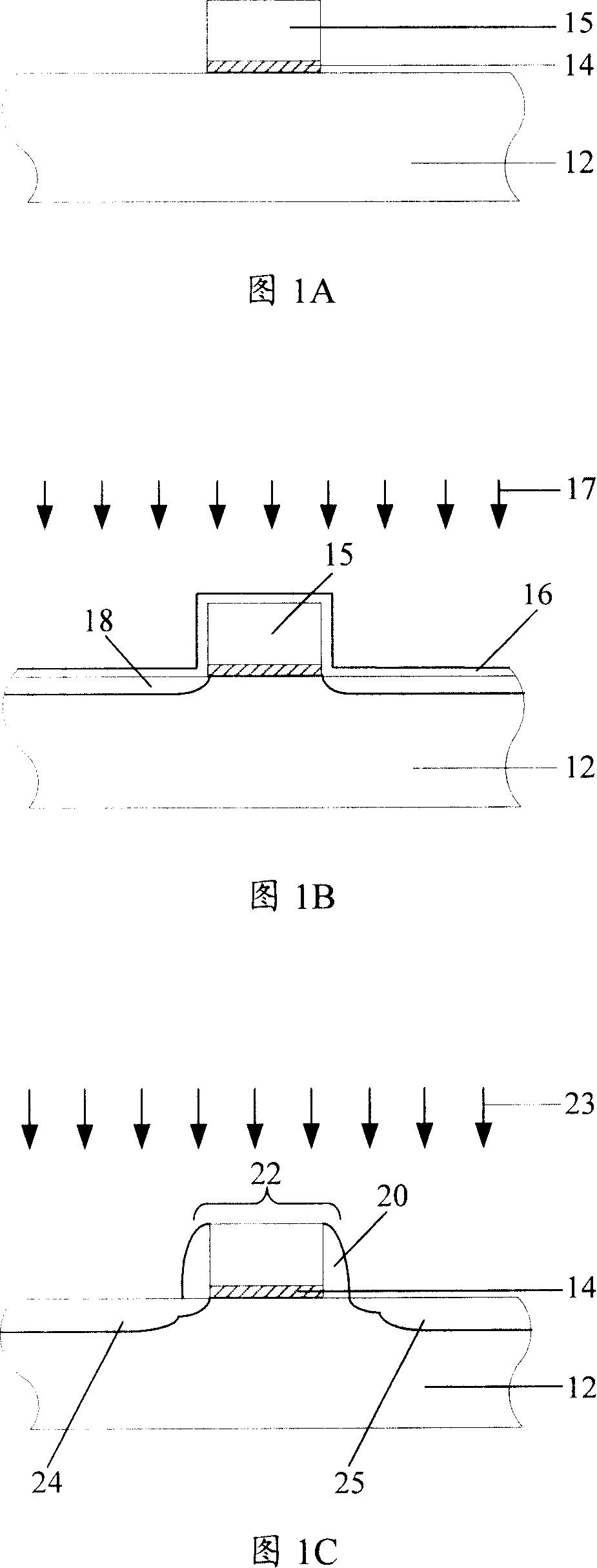

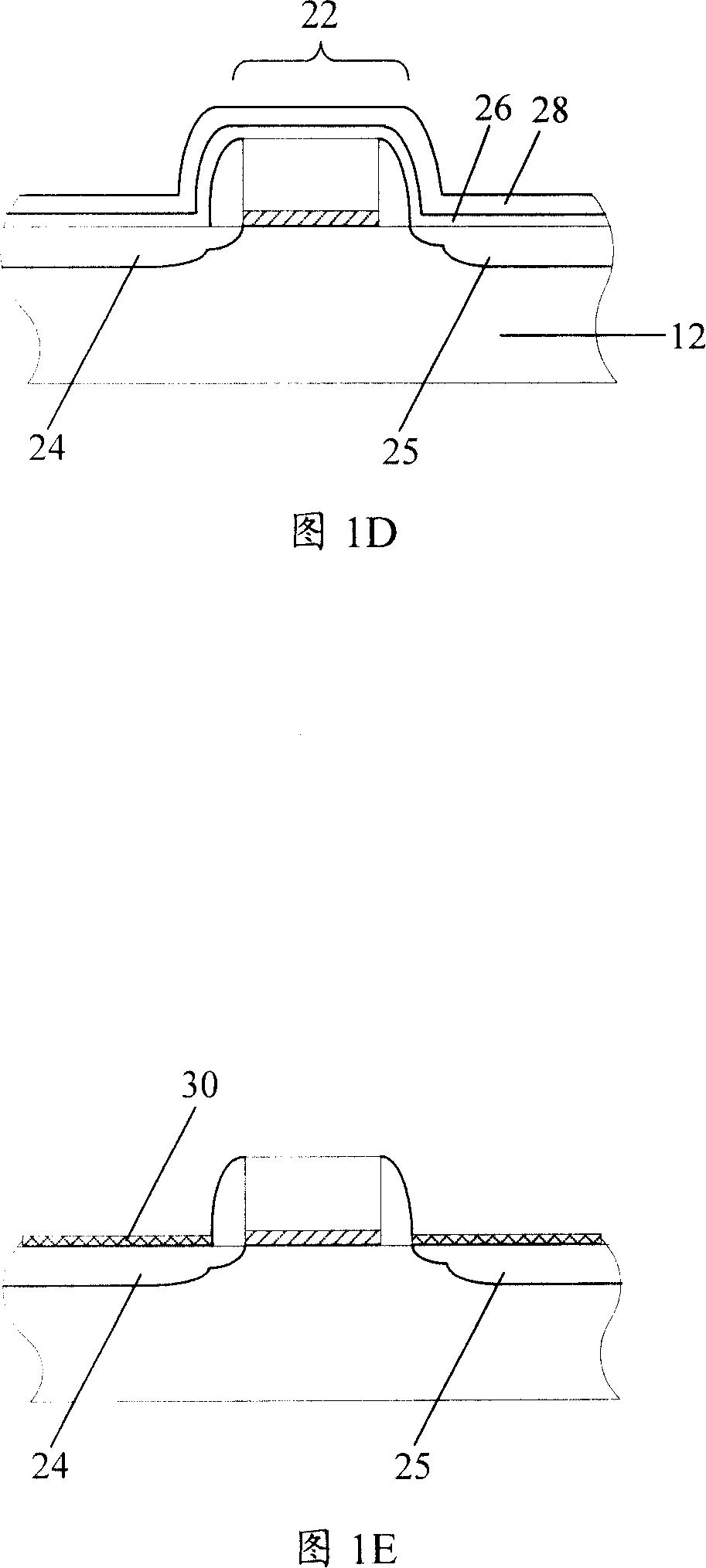

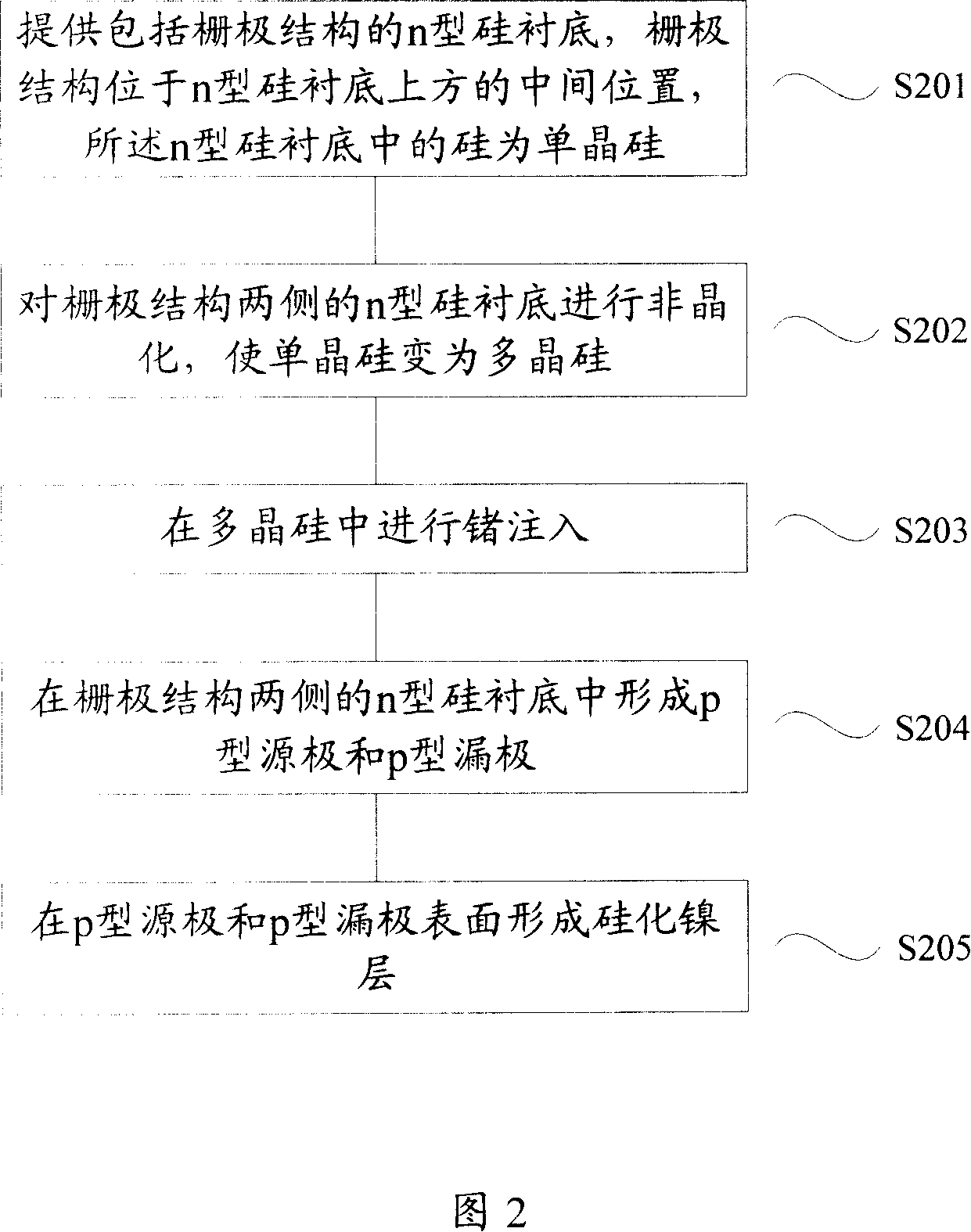

[0028] With the development of VLSI, CMOS transistors that consume less power and are suitable for high integration have been widely used in semiconductor processes. Nickel silicide is a material used in the manufacture of CMOS devices. In addition to the advantages of low resistivity and reduced silicon consumption of single silicides, it has been demonstrated that ultra-shallow junctions with plasma doping have very low junction leakage. The main obstacle to the application of nickel silicide is that nickel disilicide will be produced at the same time as nickel silicide is formed, which will form a spike and cause leakage current. Therefore, in the process of forming the PMOS transistor, especially when forming the nickel silicide layer, the present invention adds an amorphous metal implantation step so that the subsequent nickel layer reacts with the silicon substrate to form a nickel silicide layer without generating nickel disilicide , there will be no peak phenomenon, an...

PUM

| Property | Measurement | Unit |

|---|---|---|

| depth | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More