Production method of metal wiring structure

A manufacturing method and metal wiring technology, which are used in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., to achieve the effect of controlling contact resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The specific embodiments of the present invention will be described in detail below in conjunction with specific examples.

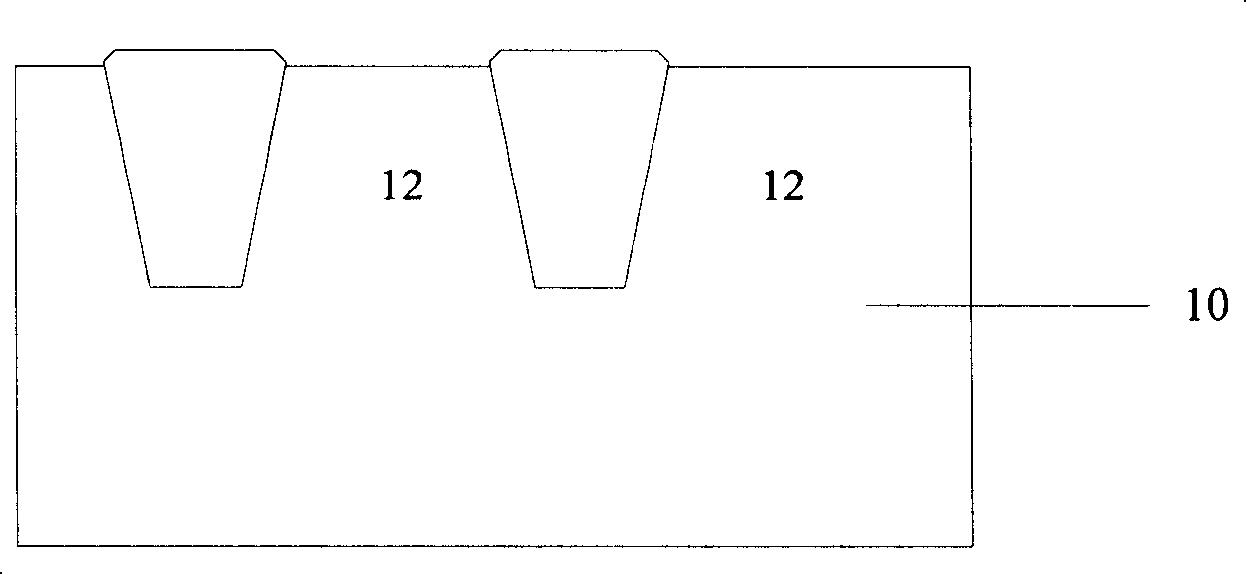

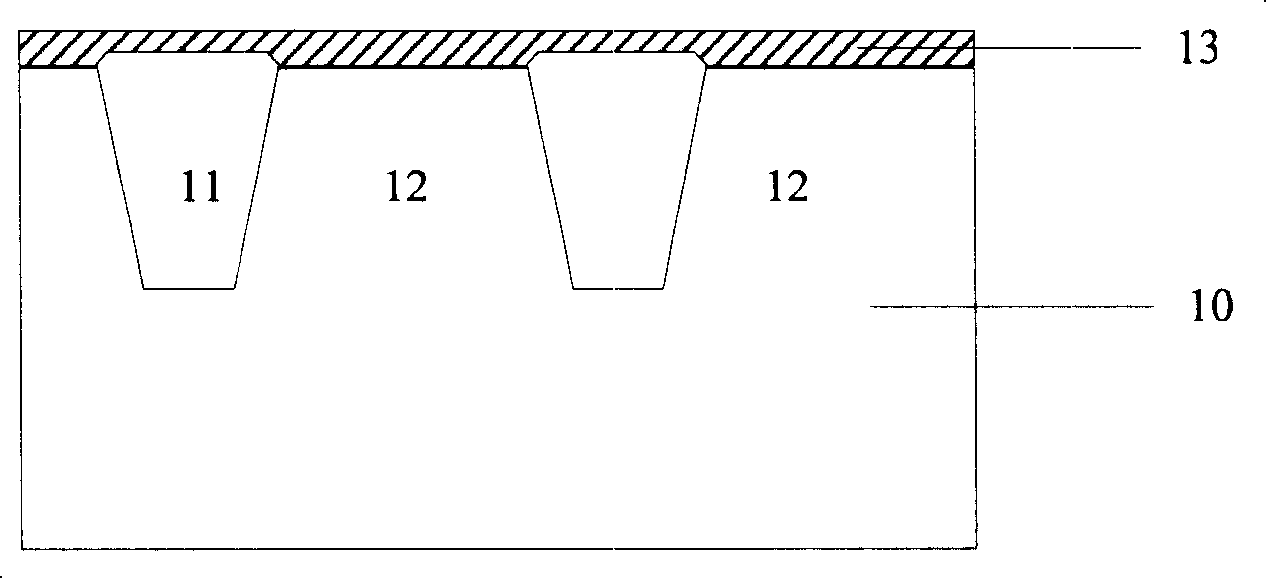

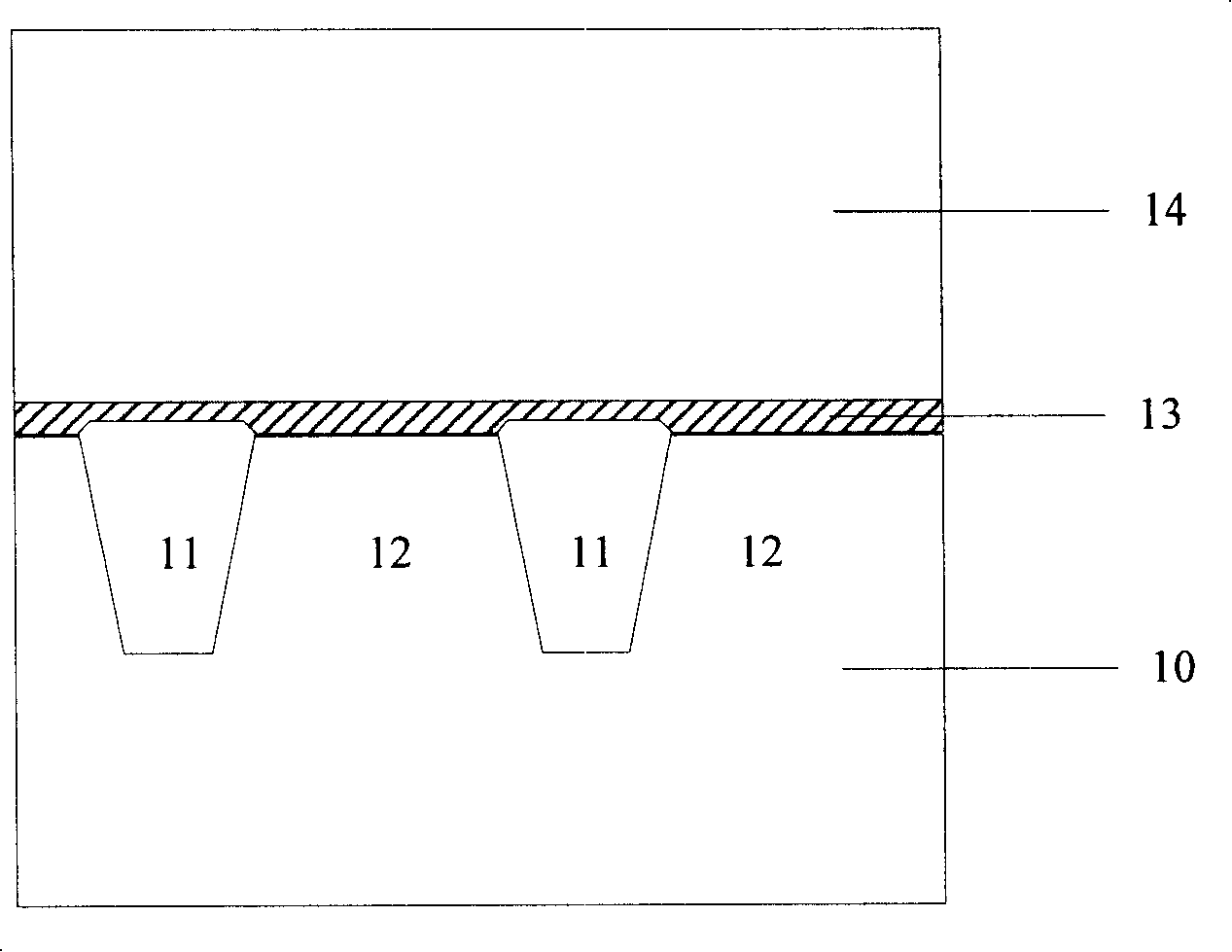

[0023] The present invention provides a method for manufacturing a metal wiring structure, which includes: providing a semiconductor substrate having an isolation structure and an active region located between the isolation structure, and the isolation structure has a corrosion barrier layer, and the active region has An insulating isolation layer; forming a first etch stop layer on the semiconductor substrate; forming a second etch stop layer on the first etch stop layer; forming an interlayer dielectric layer on the second etch stop layer; A photoresist pattern is formed on the interlayer dielectric layer; the first etching: the interlayer dielectric layer is etched with the photoresist as a mask, and stops at the second etching stop layer; the second etching: with light Resist is a mask to etch the second etch stop layer and stop at the first etch ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More