Structure of semiconductor device package and the method of the same

A packaging structure, semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve problems such as increasing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0073] The invention discloses a packaging structure of a semiconductor component. The component utilizes a substrate with defined terminal metal pads formed thereon and a predetermined groove in the substrate. A die is disposed in the die receiving groove by adhesion. A photosensitive material is coated on the die and the preformed substrate. Preferably, the photosensitive material is made of elastic material.

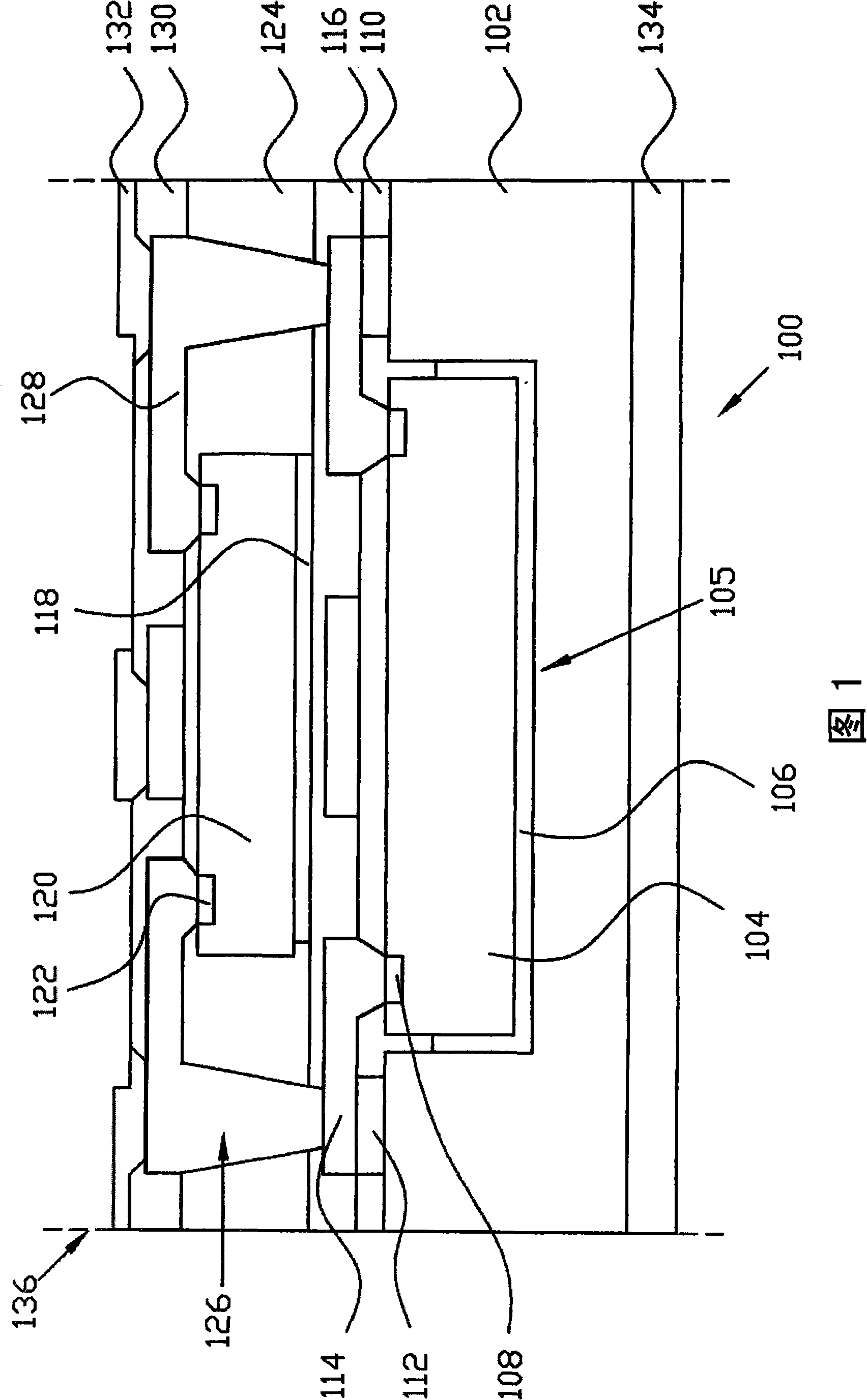

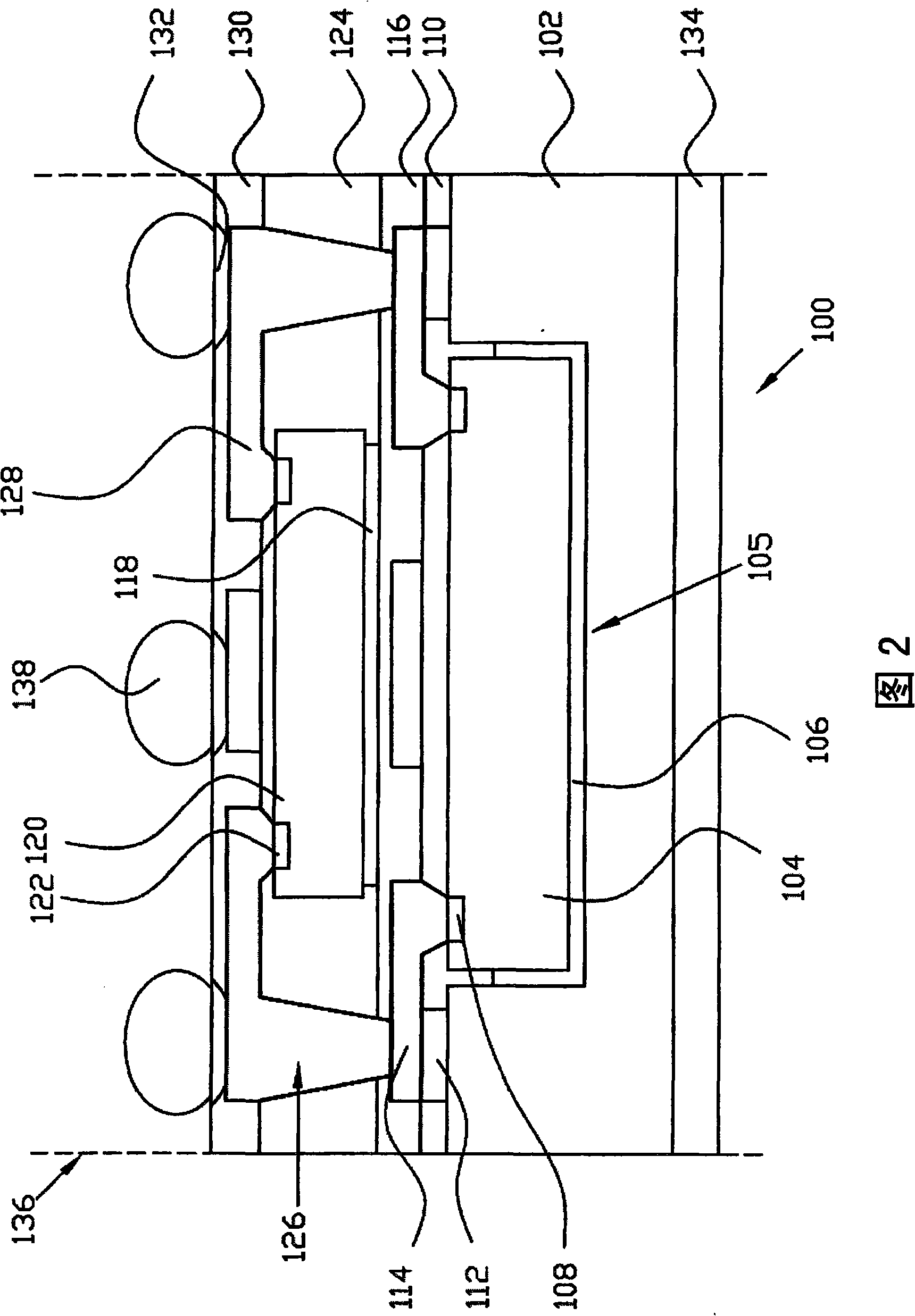

[0074] Referring to FIG. 1 , it is a cross-sectional view of a semiconductor device package according to the present invention. The semiconductor device package 100 includes: a substrate 102; a first die 104; a second die 120; a die receiving groove 105; a first die attach material 106; a second die attach material 118; a first dielectric layer 110, a second dielectric layer 116 and a third dielectric layer 130; adhesive paste 124; a through hole 126; a first redistribution layer 114; a second redistribution layer 128 ; a cover layer 134 ; terminal pad 132 ; and a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More