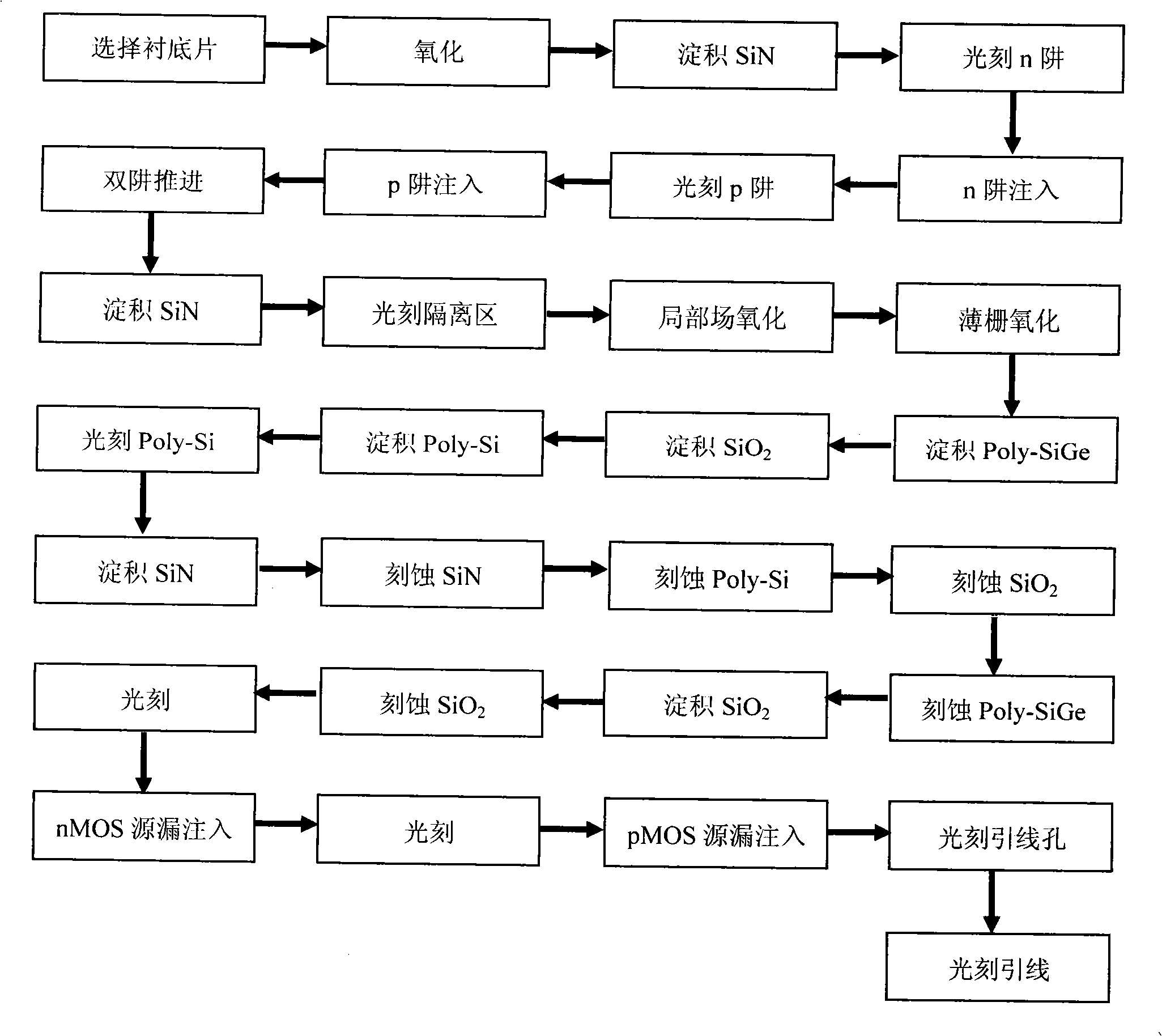

Method for preparing polycrystal SiGe gate nano-scale CMOS integrated circuit based on multilayered auxiliary structure

An auxiliary structure and integrated circuit technology, which is applied in the manufacture of circuits, electrical components, semiconductors/solid-state devices, etc., can solve the problems of limited adjustment range of device threshold voltage and increased difficulty, so as to reduce process difficulty, improve manufacturing capacity, and improve performance Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0032] Embodiment 1: the CMOS integrated circuit with the polycrystalline SiGe gate that the conductive channel is prepared on the Si substrate is 75nm, and concrete steps are as follows:

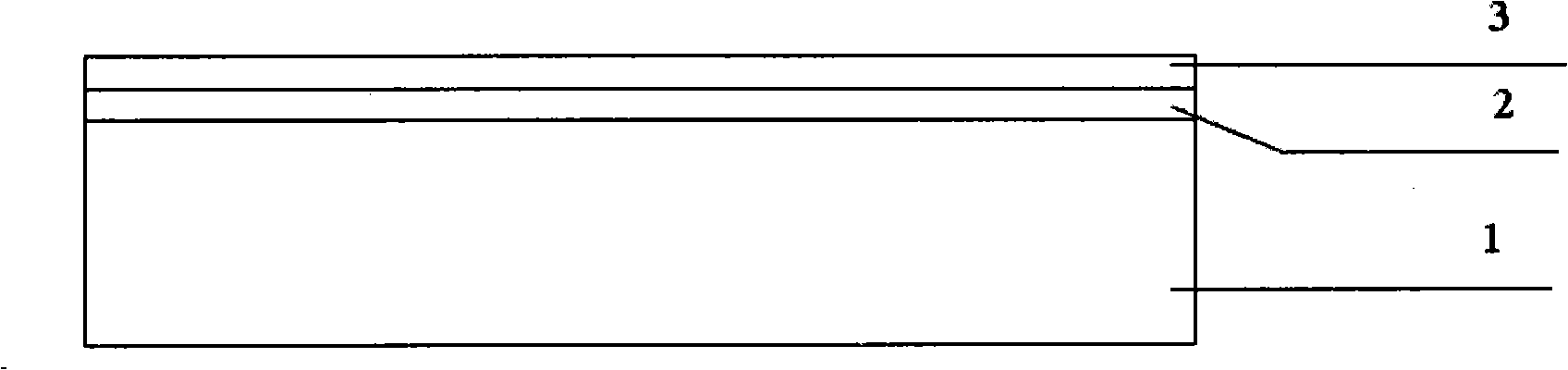

[0033] Step 1, depositing a masking layer, as shown in Figure 2(a).

[0034] (1a) Select the crystal orientation as and the doping concentration as 10 15 cm -3 Left and right p-type Si substrate sheets 1;

[0035] (1b) Thermally oxidize a layer of 25nm thick SiO on the substrate 2 buffer layer 2;

[0036] (1c) on SiO 2 A 120nm-thick SiN layer 3 is deposited on the buffer layer by plasma-enhanced chemical vapor deposition (PECVD) for the masking of well implantation.

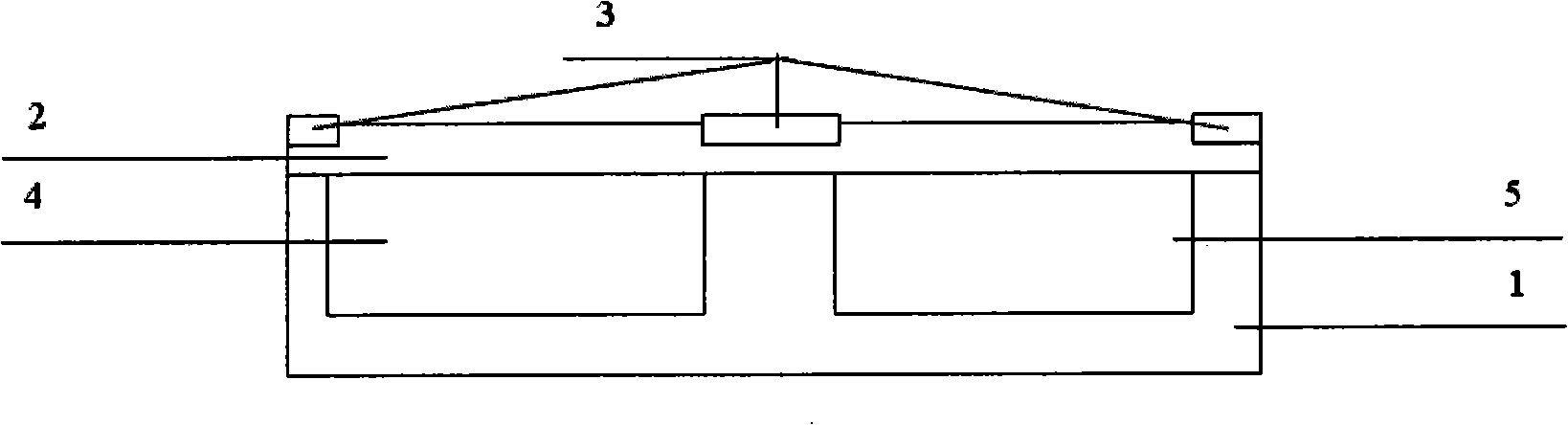

[0037] Step 2, forming a well region, as shown in FIG. 2(b).

[0038] (2a) Photoetching the P well region 4 and the N well region 5 on the SiN layer 3 according to the phase sequence;

[0039] (2b) Boron is implanted in the P well region to form a p-type region, and SiO is thermally oxidized on the surface of the P well ...

Embodiment 2

[0068] Embodiment 2: on the SOI substrate, the CMOS integrated circuit with the polycrystalline SiGe gate with a 65nm conductive channel is prepared, and the specific steps are as follows:

[0069] Step 1, depositing a masking layer, as shown in Figure 2(a).

[0070] (1a) Select the crystal orientation as and the doping concentration as 10 15 cm -3 left and right p-type SOI substrates 1;

[0071] (1b) Thermally oxidize a layer of SiO with a thickness of 15 nm on the substrate 2 buffer layer 2;

[0072] (1c) on SiO 2 A 100nm-thick SiN layer 3 is deposited on the buffer layer by atmospheric pressure chemical vapor deposition (APCVD) for the masking of well implantation.

[0073] Step 2, forming a well region, as shown in FIG. 2(b).

[0074] (2a) Photoetching the P well region 4 and the N well region 5 on the SiN layer 3 according to the phase sequence;

[0075] (2b) Boron is implanted in the P well region to form a p-type region, and SiO is thermally oxidized on the surf...

Embodiment 3

[0104] Embodiment 3: the CMOS integrated circuit with the polycrystalline SiGe gate that the conductive channel is 90nm is prepared on the Si substrate, the specific steps are as follows:

[0105] Step 1, depositing a masking layer, as shown in Figure 2(a).

[0106] (1a) Select the crystal orientation as and the doping concentration as 10 15 cm -3 Left and right p-type Si substrate sheets 1;

[0107] (1b) Thermally oxidize a layer of SiO with a thickness of 35 nm on the substrate 2 buffer layer 2;

[0108] (1c) on SiO 2 A 130nm-thick SiN layer 3 is deposited on the buffer layer by means of low-pressure chemical vapor deposition LPCVD, which is used for the masking of well implantation.

[0109] Step 2, forming a well region, as shown in FIG. 2(b).

[0110] (2a) Photoetching the P well region 4 and the N well region 5 on the SiN layer 3 according to the phase sequence;

[0111] (2b) Boron is implanted in the P well region to form a p-type region, and SiO is thermally ox...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More