Hardware method for memory management core related to schedule performance

A memory management and hardware-based technology, applied in the field of hardware-based process memory management cores, can solve problems such as tampering and insufficient security, reduce overhead, eliminate the possibility of malicious tampering, and ensure complete accuracy and reliability. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

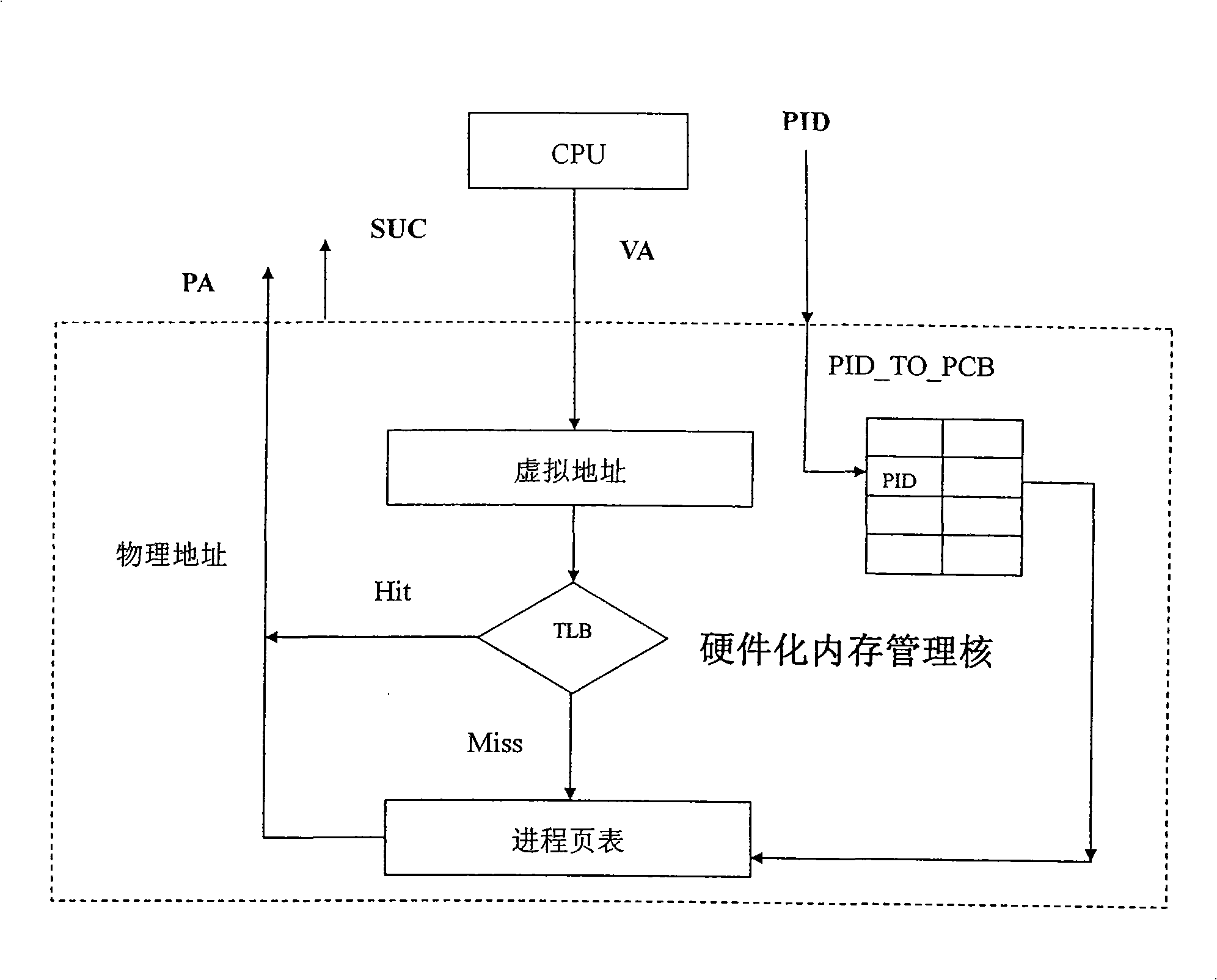

[0037] The present invention will be further described below in conjunction with drawings and embodiments.

[0038] First explain the nouns used and the premises used in some technical designs:

[0039] PID: process number, 4bit, 0 is not used, so it can represent up to 15 processes;

[0040] PID_TO_PCB: process number and page table base address conversion table;

[0041] suc: the return value of each operation in the output signal, 1 for success and 0 for failure;

[0042] VA: Logical address in the input signal, a total of 22 bits, page size 4K bytes;

[0043] PA: The physical address in the output signal, with a total of 22 bits and a page size of 4K bytes;

[0044] last_pid: the process number of the last running or about to be switched away;

[0045] curr_pid: the number of the process currently running or about to run;

[0046] TLB: Translation Look-aside Buffer, used to speed up page table lookup;

[0047] The method of hardwareizing the memory management core di...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More