Method for carbon nano tube to achieve vertical interconnection of upper and lower layers of conductive material

A conductive material, carbon nanotube technology, applied in the field of interconnection, can solve the problems of poor quality control of carbon nanotubes, growth temperature can not be too low, non-compliance, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

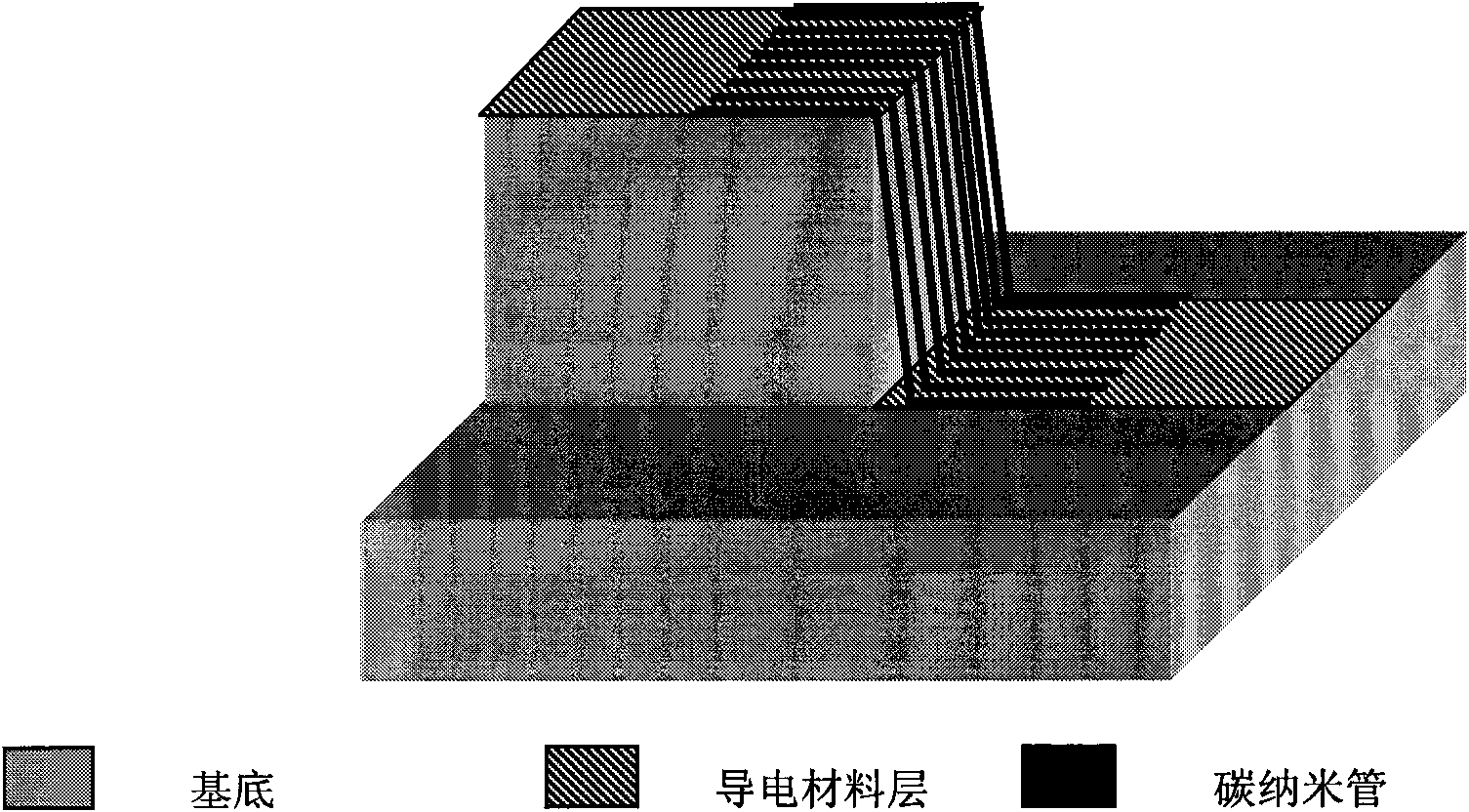

[0025] Embodiment one, with figure 1 The shown vertical structure of the boss type is taken as an example to illustrate the process of the present invention.

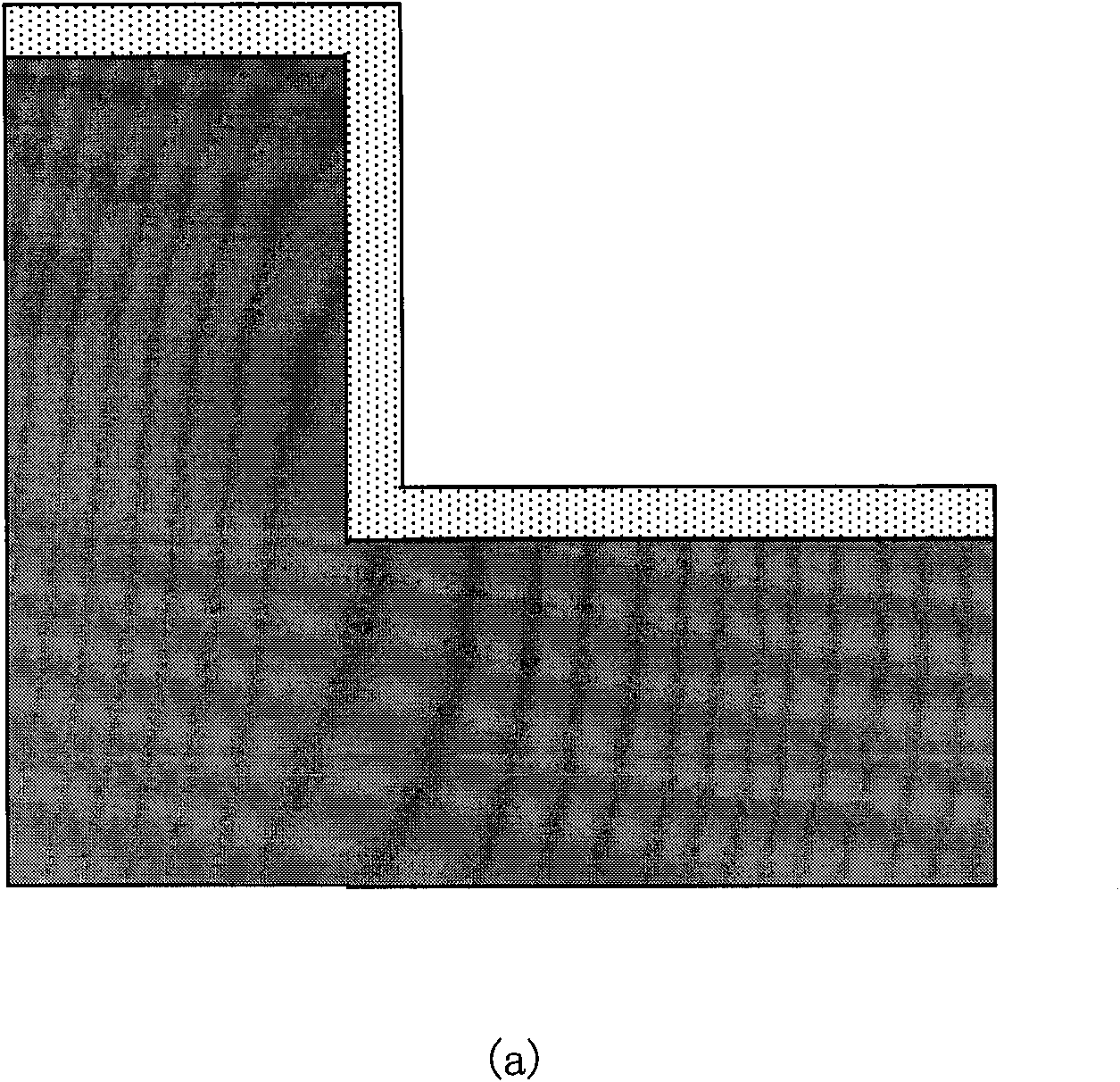

[0026] 1) First, etch a boss structure on the silicon substrate. There is a vertical plane between the upper surface and the lower surface of the structure. A layer of stunning dielectric layer can be deposited on the above-mentioned boss structure, such as figure 2 (a) shown.

[0027] The substrate can be a semiconductor material such as Si, Ge, GaAs, or an integrated circuit structure.

[0028] The above insulating dielectric layer can be SiO 2 , Organic, nitrogen-doped oxides or porous low-K dielectric materials.

[0029] 2) depositing a conductive layer on the vertical structure;

[0030] The upper and lower layers of conductive materials can be the same material or different materials, including but not limited to metals, highly doped semiconductor materials: Si, Ge, GaAs, carbon nanotube films or conductive p...

Embodiment 2

[0038] Embodiment two, with image 3 The groove-type vertical structure shown is taken as an example to illustrate the process of the present invention.

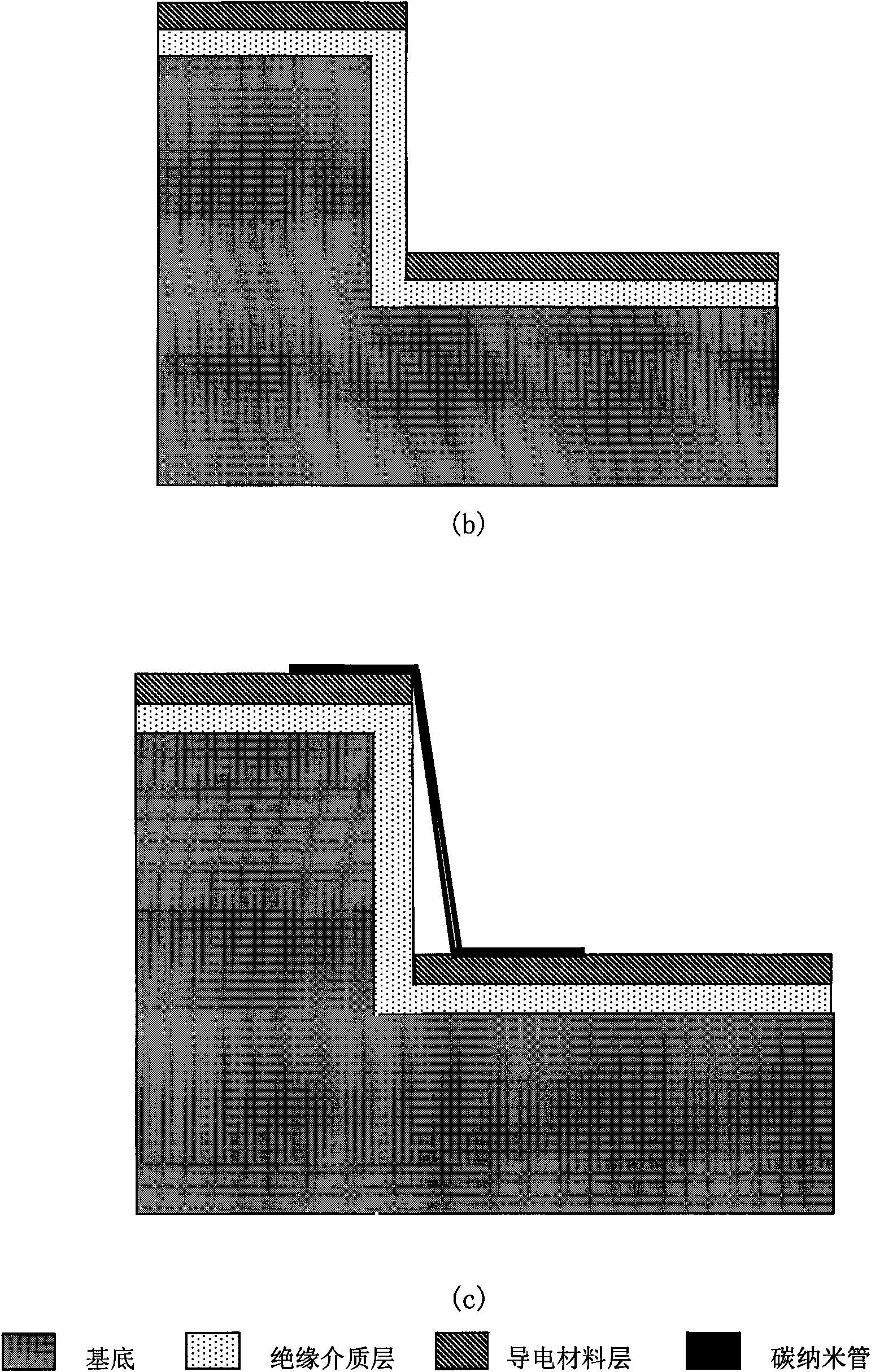

[0039] 1) First, etch a groove structure on the substrate, three vertical planes are arranged between the upper surface and the lower surface of the structure, and a layer of insulating dielectric layer can be deposited on the above-mentioned vertical structure, such as image 3 (a) shown.

[0040] The substrate can be a semiconductor material such as Si, Ge, GaAs, or any vertical structure of an integrated circuit; material 2 is an insulating dielectric material, which can be SiO 2 , Organic, nitrogen-doped oxides or porous low-K dielectric materials.

[0041] 2) Deposit a conductive layer on the upper and lower two-layer structure;

[0042] The deposited conductive layer can be metals such as Ti / Au, or highly doped semiconductor materials such as Si, Ge, GaAs, etc., as shown in 3(b).

[0043] The conductive materials o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More