Polysilicon membrane forming method and polysilicon gate forming method

A polysilicon film and polysilicon layer technology, which is applied in the directions of polysilicon material growth, chemical instruments and methods, crystal growth, etc., can solve the problem that the polysilicon film cannot take into account the flatness and interface quality, etc., so as to improve the physical and electrical characteristics, Improved formation quality, improved grain size effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

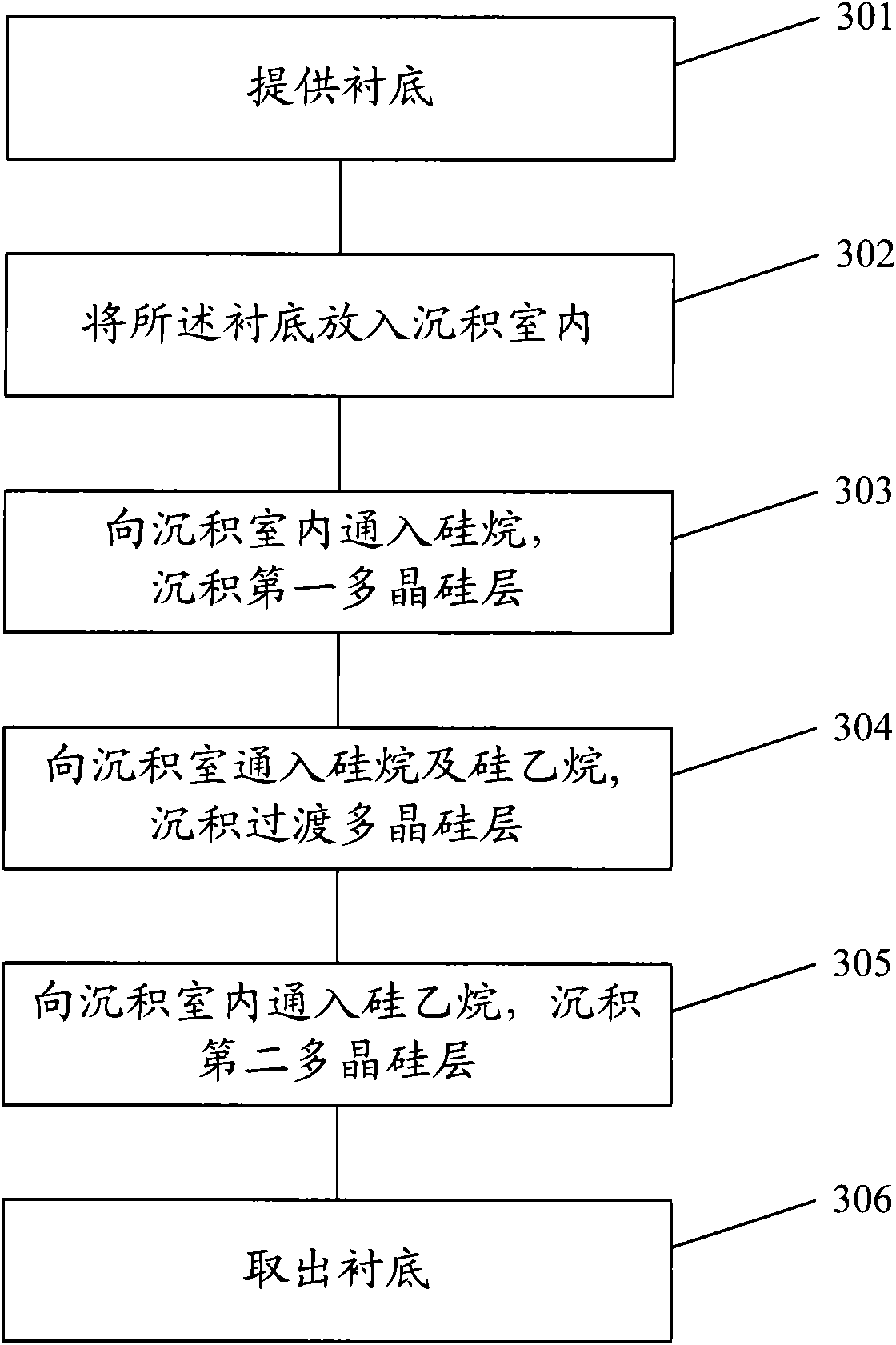

[0069] The first embodiment of the present invention introduces a new method for forming a polysilicon film, image 3 It is a flow chart of the method for forming a polysilicon thin film in the first embodiment of the present invention, Figure 4 to Figure 6 In order to illustrate the device cross-sectional view of the method for forming a polysilicon film in the first embodiment of the present invention, the following is combined Figure 3 to Figure 6 The first embodiment of the present invention will be described in detail.

[0070] Step 301: Provide a substrate.

[0071] The substrate in this embodiment can be a simple silicon substrate, or a substrate with a certain structure formed, for example, a silicon oxide layer can be formed on the surface of the substrate. In addition, in other embodiments of the present invention, the substrate can also be made of other materials, such as germanium material, gallium arsenide material or silicon carbide material.

[0072] Step 3...

no. 2 example

[0102] The second embodiment of the present invention introduces a new gate forming method, Figure 7 is a flow chart of the gate formation method in the second embodiment of the present invention, Figure 8 to Figure 13 In order to illustrate the device cross-sectional view of the gate forming method in the second embodiment of the present invention, the following is combined with Figure 7 to Figure 13 The second embodiment of the present invention will be described in detail.

[0103] Step 701: providing a substrate on which a gate oxide layer has been formed.

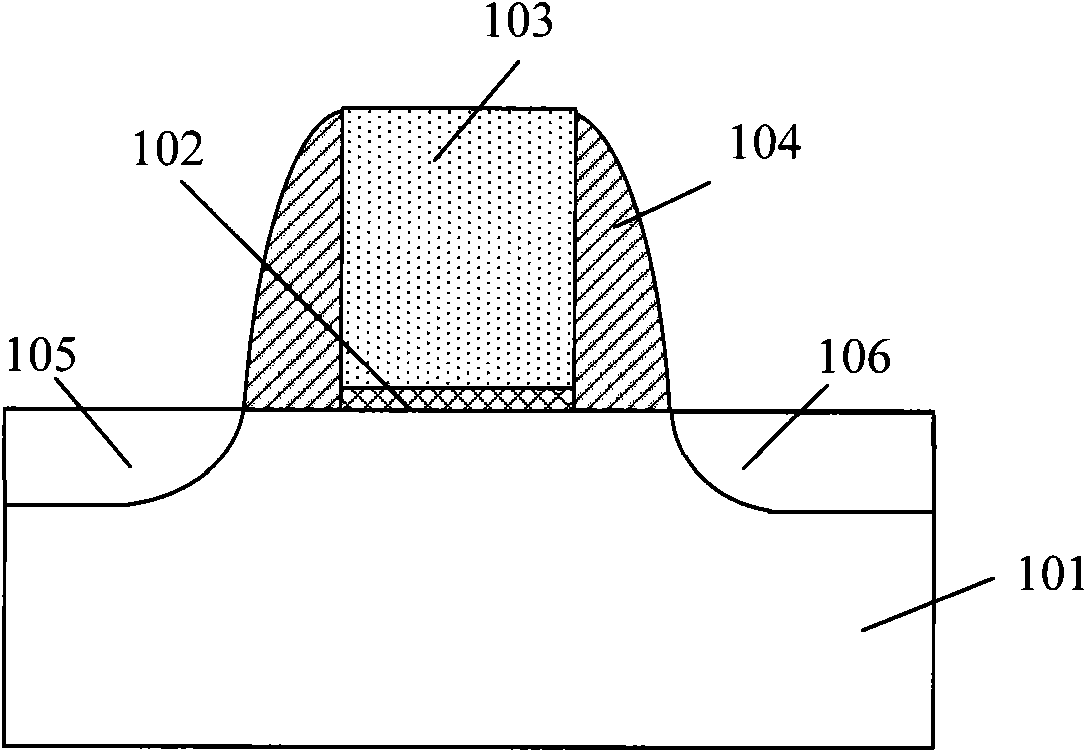

[0104] Figure 8 It is a schematic cross-sectional view of the substrate in the second embodiment of the present invention, as Figure 8 As shown, the substrate in this embodiment includes a silicon substrate 801 and a gate oxide layer 802 thereon. In other embodiments of the present invention, the silicon substrate 801 may also be a substrate of other materials, Such as germanium materials, gallium arsenide mat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More