Flattening method of interlayer medium layer and forming method of contact hole

A technology of interlayer dielectric layer and planarization method, which is applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of poor contact hole formation quality and consistency, and achieve the effect of meeting high requirements and high flatness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

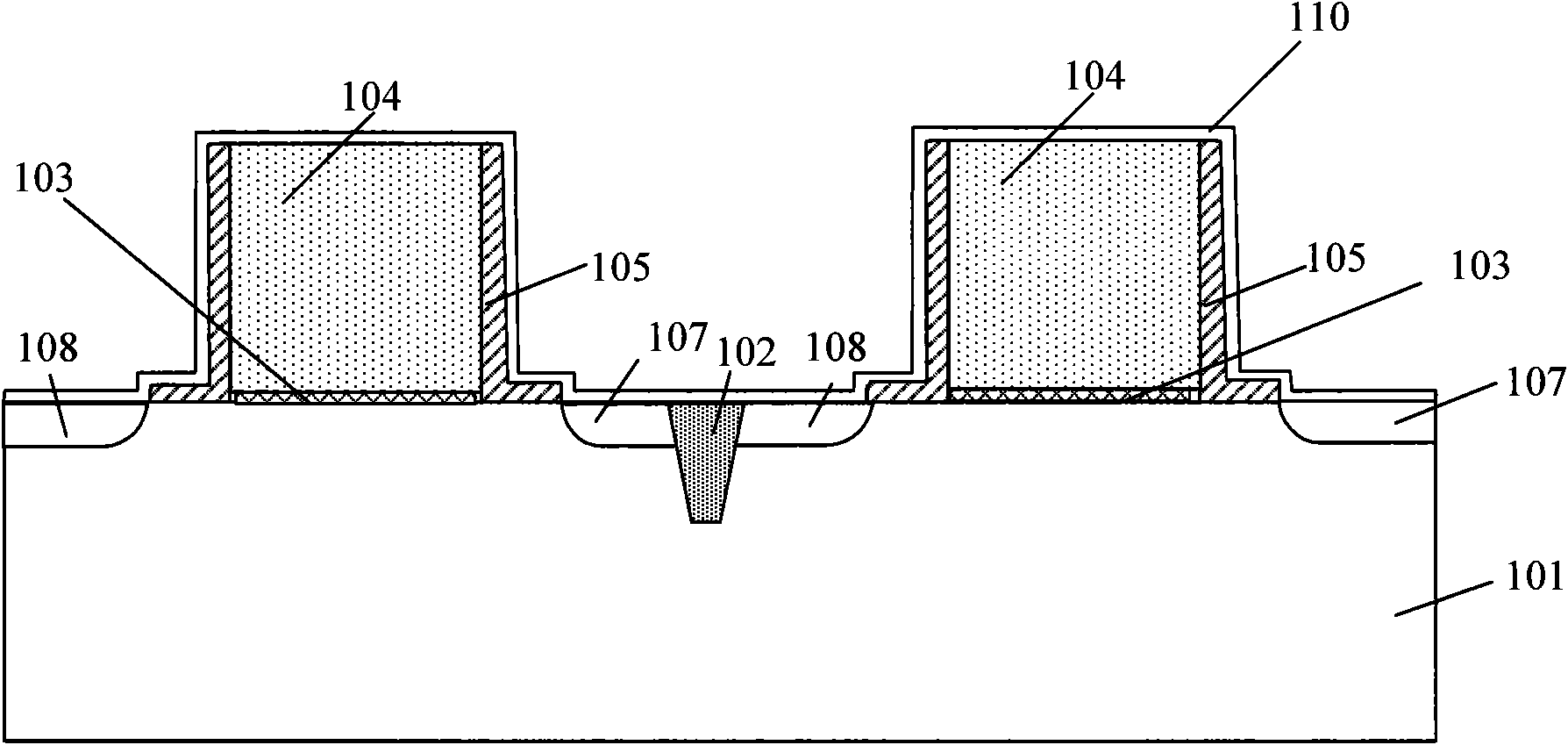

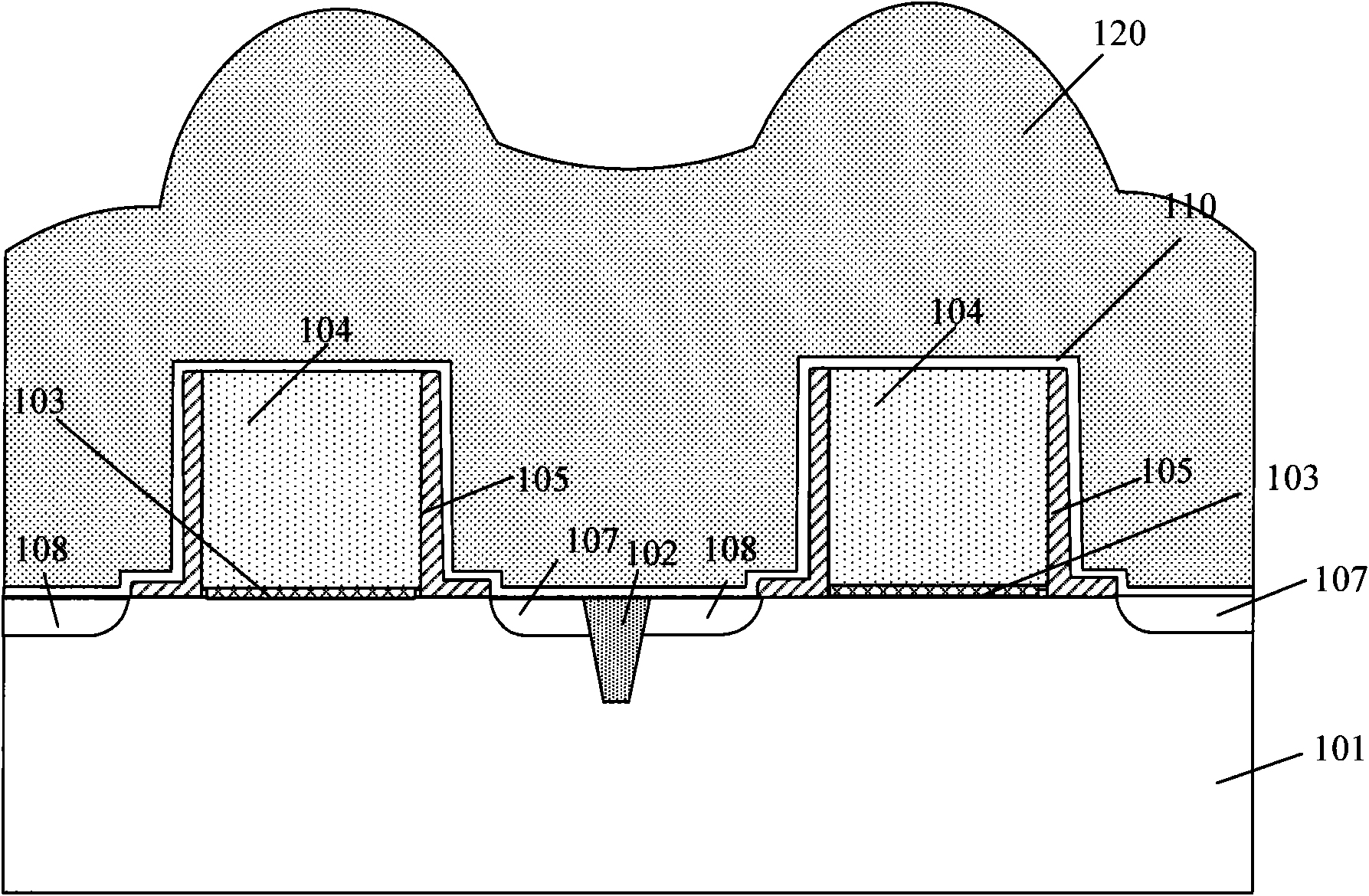

[0064] Figure 5 is a flow chart of the method for planarizing the interlayer dielectric layer in the first embodiment of the present invention, Figure 6 to Figure 9 In order to illustrate the cross-sectional view of the device of the method for planarizing the interlayer dielectric layer in the first embodiment of the present invention, the following is combined with Figure 5 to Figure 9 The first embodiment of the present invention will be described in detail.

[0065] Step 501: Provide a substrate, and the substrate already has a gate structure.

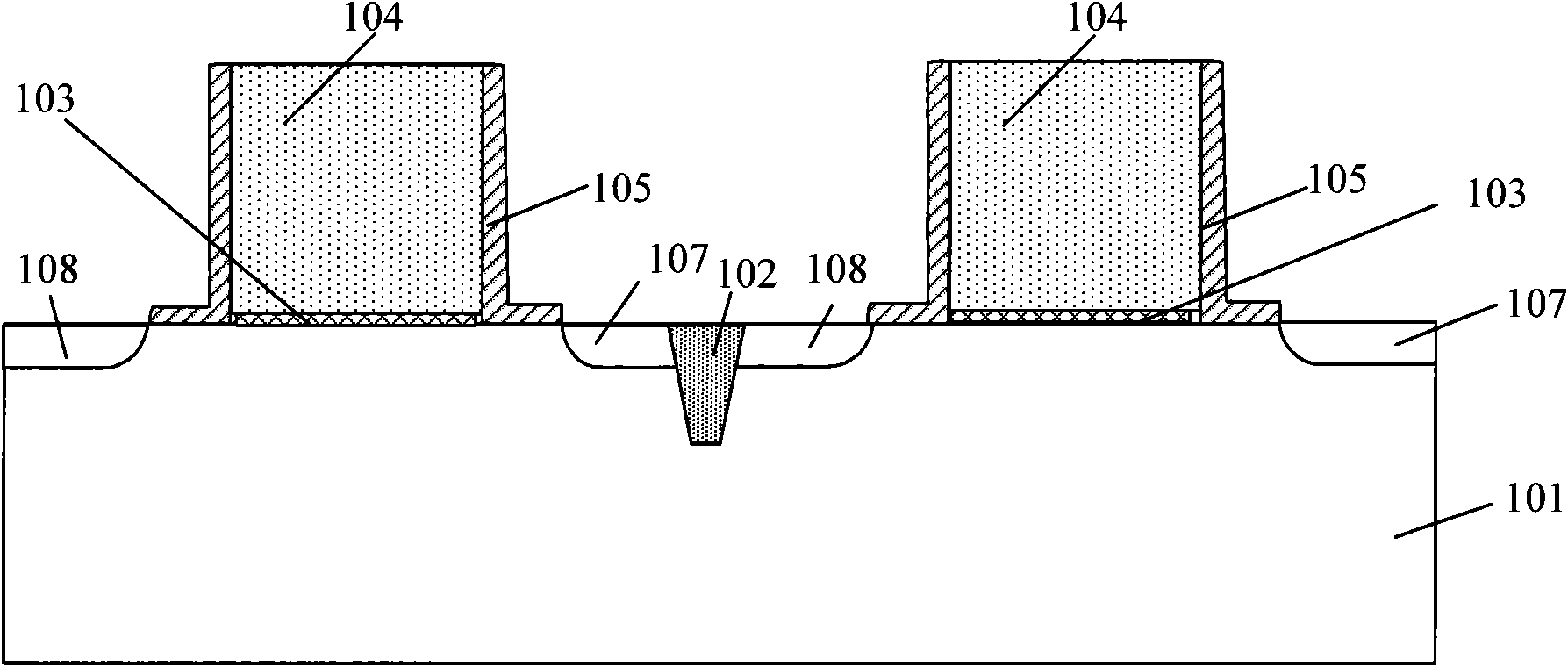

[0066] Figure 6 It is a schematic cross-sectional view of the substrate used in the first embodiment of the present invention, such as Figure 6 As shown, the structure of the substrate is as follows: a gate 604 with a gate oxide layer (GateOxide) 603 at the bottom is formed on a silicon substrate 601, and isolation trenches 602 are formed between each device; A gate sidewall layer 605 is formed on the silicon substrate 601...

no. 2 example

[0087] Figure 10 It is a flowchart of a method for forming a contact hole in the second embodiment of the present invention, Figure 11 to Figure 16 In order to illustrate the cross-sectional view of the device of the method for forming the contact hole of the second embodiment of the present invention, the following is combined with Figure 10 to Figure 16 The second embodiment of the present invention will be described in detail.

[0088] Step 1001: Provide a substrate, and the substrate already has a gate structure.

[0089] Figure 11 It is a schematic cross-sectional view of the substrate used in the second embodiment of the present invention, such as Figure 11 As shown, the structure of the substrate is as follows: a gate 1104 with a gate oxide layer (GateOxide) 1103 at the bottom is formed on a silicon substrate 1101, and isolation trenches 1102 are formed between each device; A gate sidewall layer 1105 is formed on the silicon substrate 601 to achieve good protec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More