Trench gate metal oxide semiconductor field effect transistor and manufacturing method thereof

An oxide semiconductor and field effect transistor technology, which is applied in the structural field of metal oxide semiconductor field effect transistors, can solve problems such as inconvenience, transistor failure, coverage, etc., and achieves the effects of technological progress, manufacturing method improvement, and manufacturing method enhancement.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

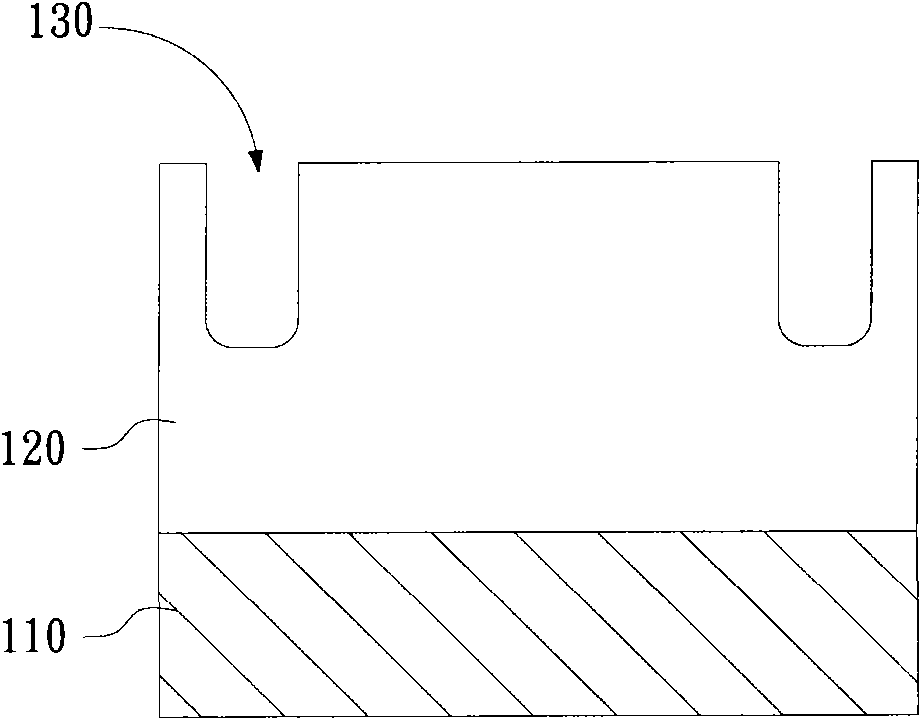

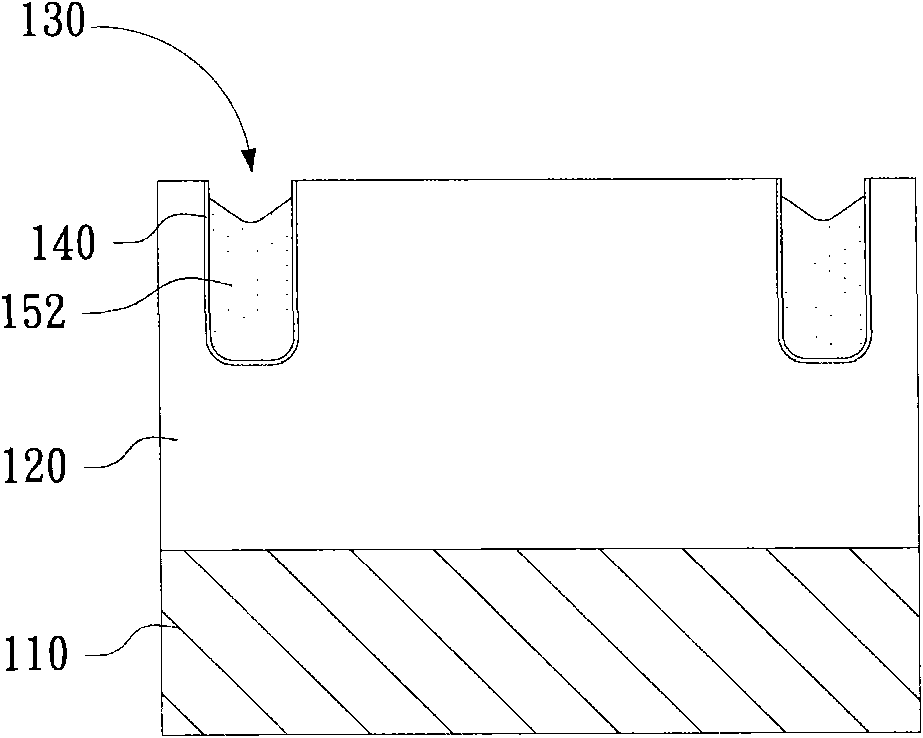

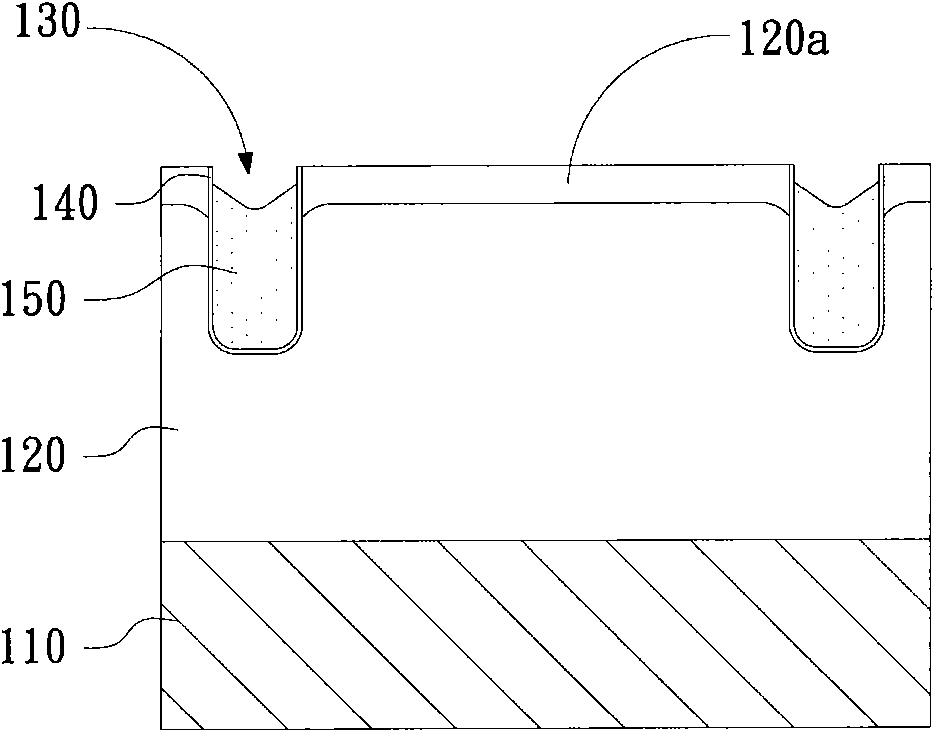

[0069] In order to further illustrate the technical means and effects that the present invention adopts to achieve the intended invention purpose, the trench-gate metal-oxide-semiconductor field-effect transistor and its manufacturing method according to the present invention are described below in conjunction with the accompanying drawings and preferred embodiments. The specific implementation, structure, manufacturing method, steps, features and effects thereof are described in detail below.

[0070] The aforementioned and other technical contents, features and effects of the present invention will be clearly presented in the following detailed description of preferred embodiments with reference to the drawings. Through the description of the specific implementation mode, when the technical means and functions adopted by the present invention to achieve the predetermined purpose can be obtained a deeper and more specific understanding, but the accompanying drawings are only f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More