Soi wafer manufacturing method

一种制造方法、芯片的技术,应用在半导体/固态器件制造、电气元件、电固体器件等方向,达到膜厚均匀性高、抑制导电型和电阻率等的变动的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1~4

[0102] (Examples 1 to 4, Comparative Examples 1 and 2)

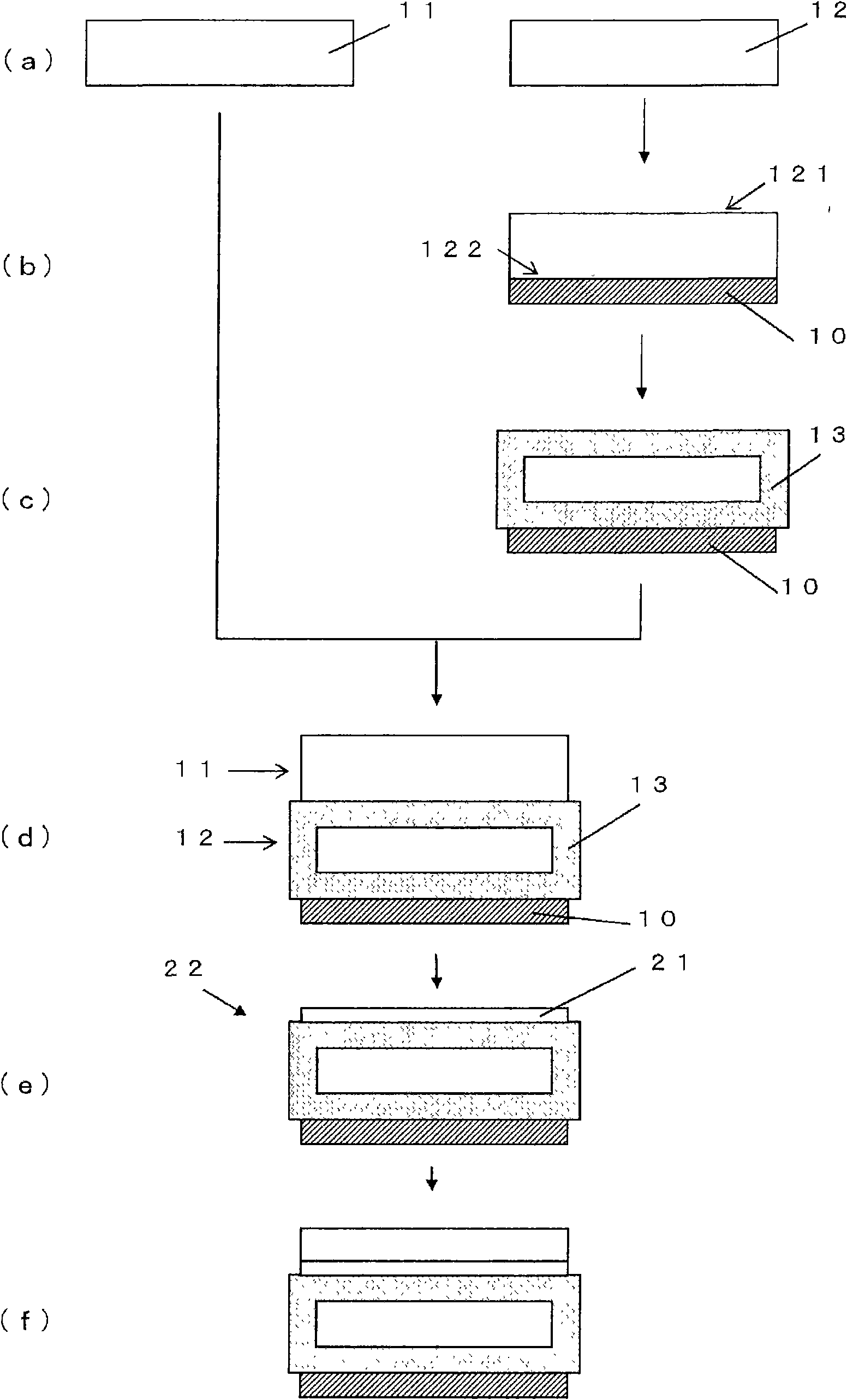

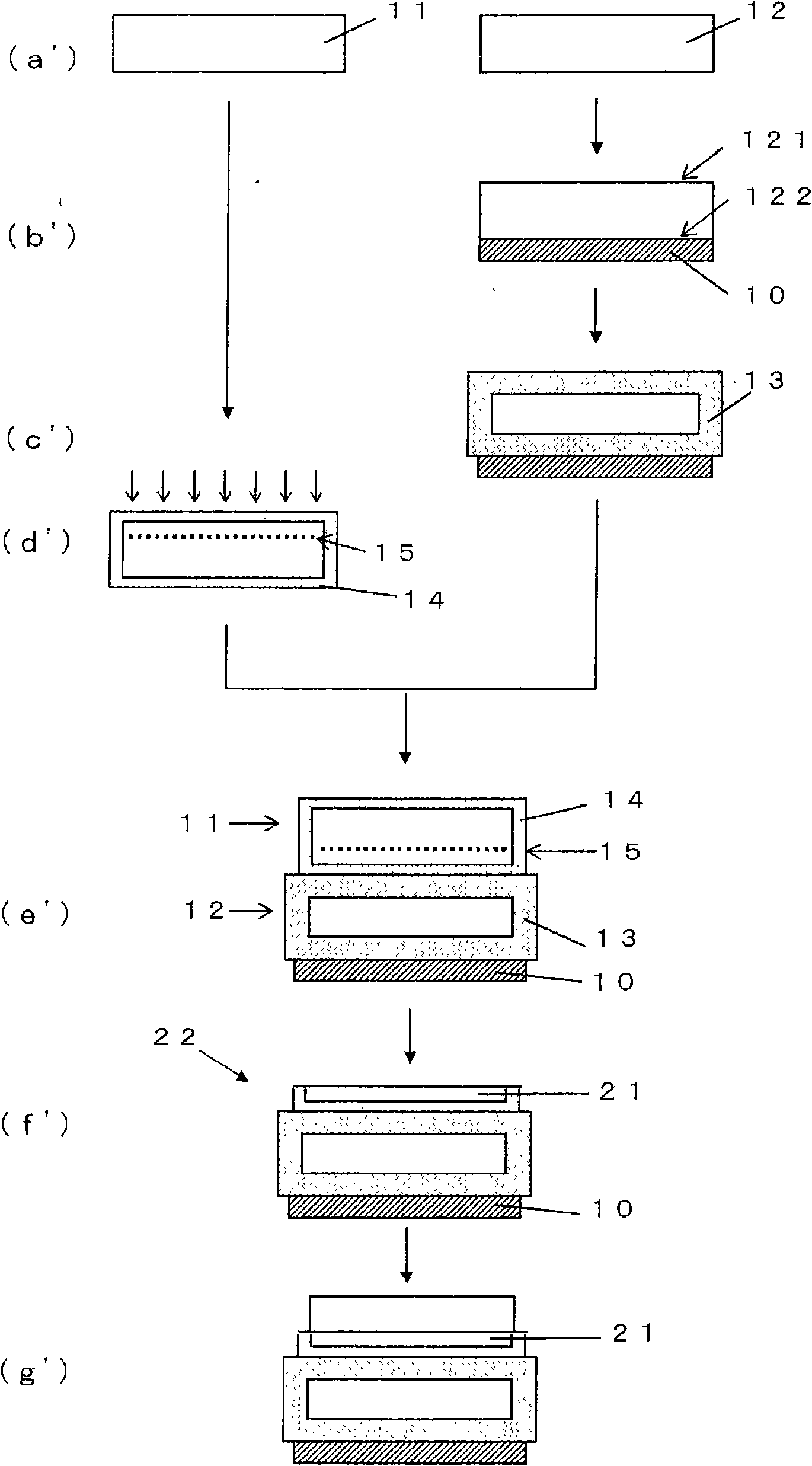

[0103] use figure 1 Fabrication of the SOI chip 22 is carried out using the flow shown. The main production conditions and results at this time are shown in Table 1 and explained below.

[0104] [Table 1]

[0105]

[0106]

[0107] First, as the bonding chip 11, prepare a 200 mm in diameter, phosphorus-doped n-type single crystal silicon chip, and as the base chip 12, prepare a 200 mm in diameter, p-type, boron-doped (6×10 18 atoms / cm 3 ) of p + Single crystal silicon chips (Examples 1 to 4, Comparative Examples 1 and 2).

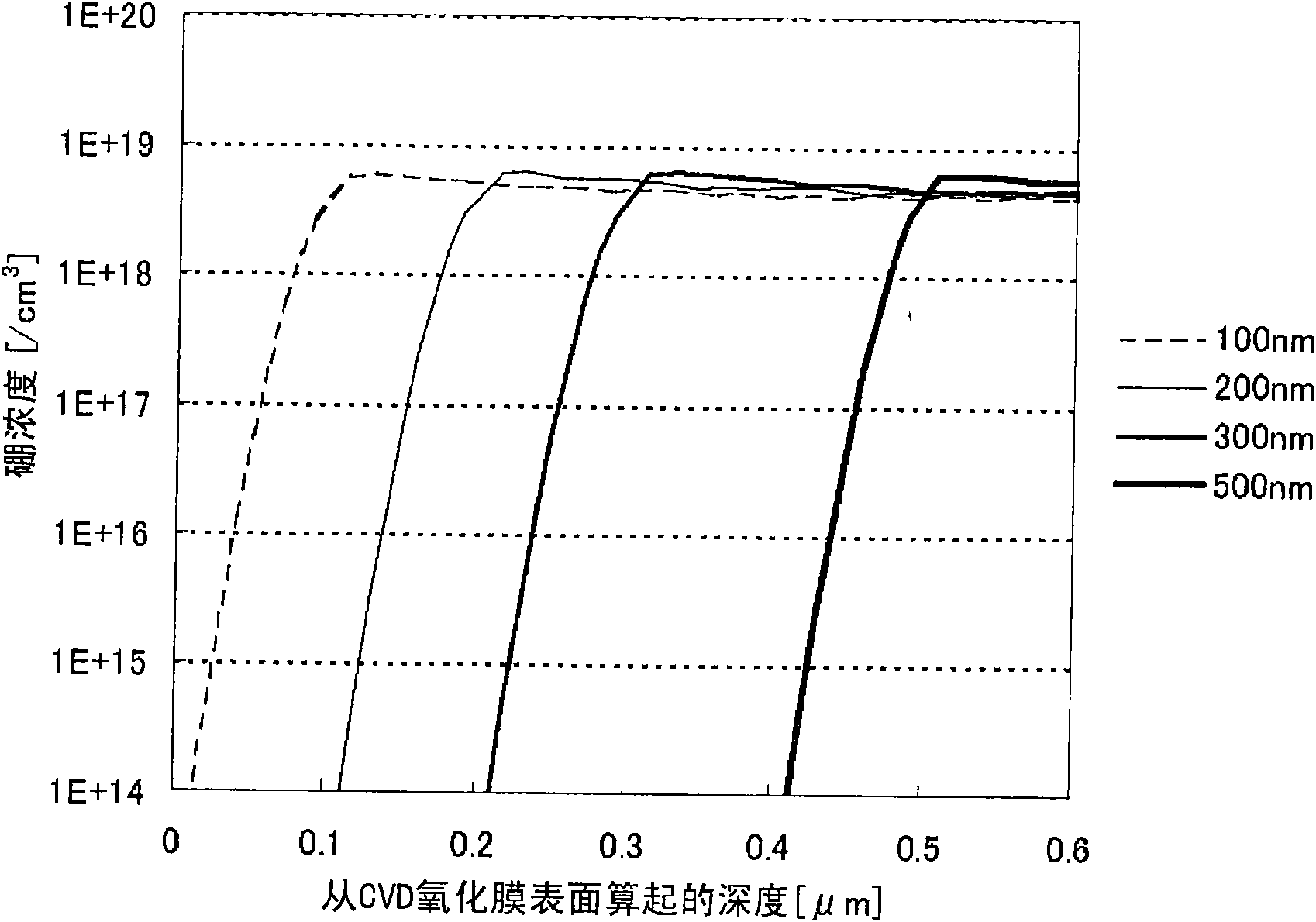

[0108] Next, place the base chip 12 on the receiving body of the CVD furnace with the bonding surface 121 facing down, and form a CVD oxide layer as the CVD insulating film 10 on the opposite surface 122 by the CVD method. membrane. The thickness of the formed CVD oxide film was 100nm in Example 1, 200nm in Example 2, 300nm in Example 3, and 500nm in Example 4. In addition, in Comparat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com