Optimization method and optimization system for memory access in multi-core system

A technology of multi-core system and optimization method, which is applied in the direction of memory system, memory address/allocation/relocation, instrument, etc. It can solve the problem of well-optimized programs without considering line cache conflicts between programs in multi-core systems, and cannot be given by different programs. And other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

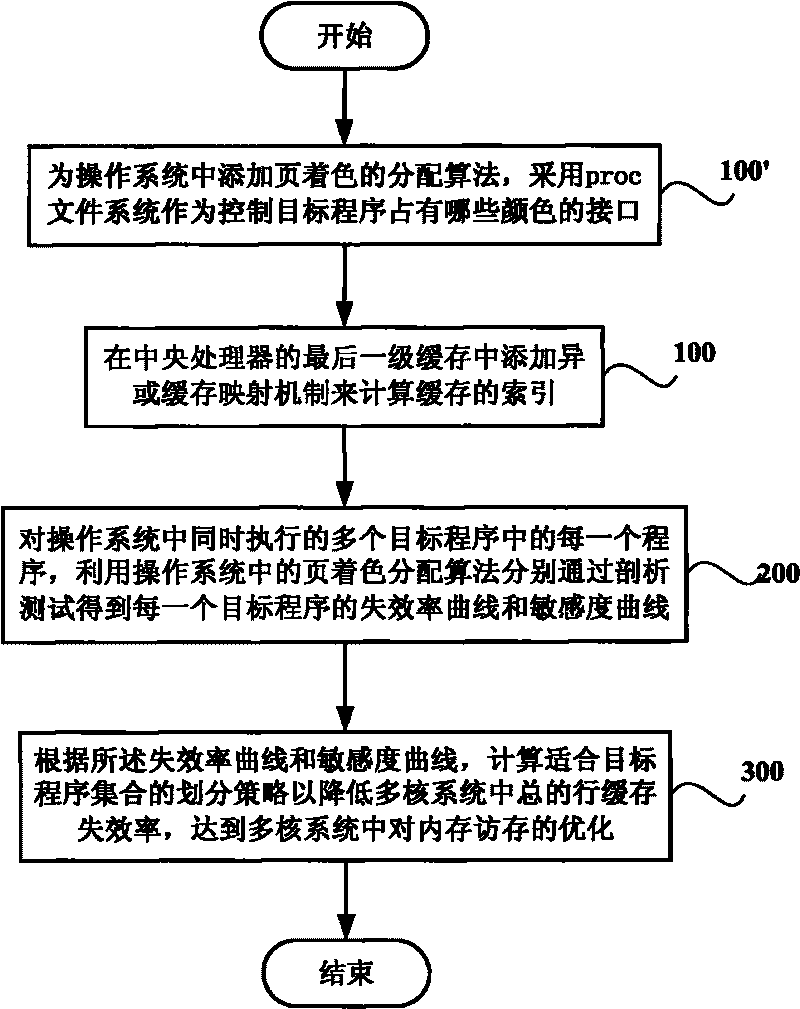

[0073] In order to make the objectives, technical solutions, and advantages of the present invention clearer, the following describes in further detail a method and system for optimizing memory access in a multi-core system of the present invention with reference to the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, but not to limit the present invention.

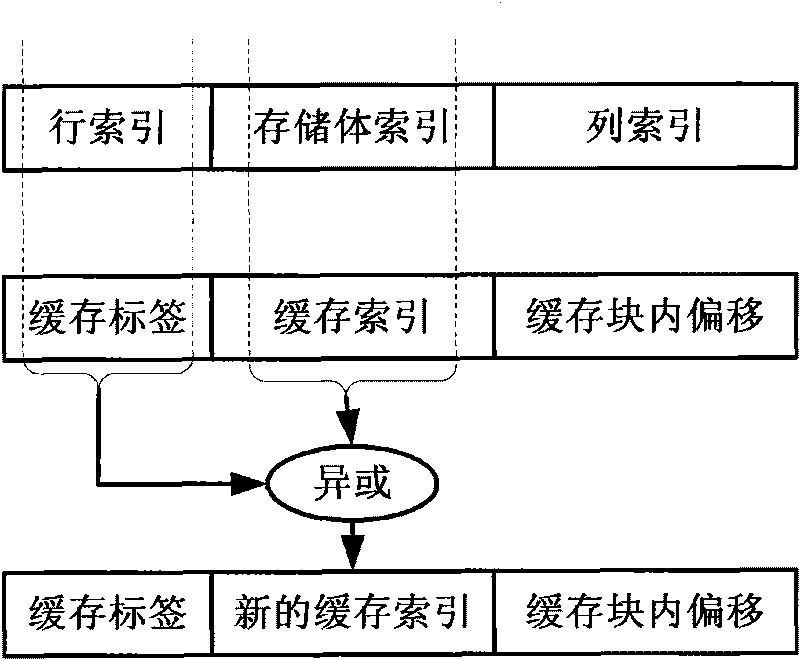

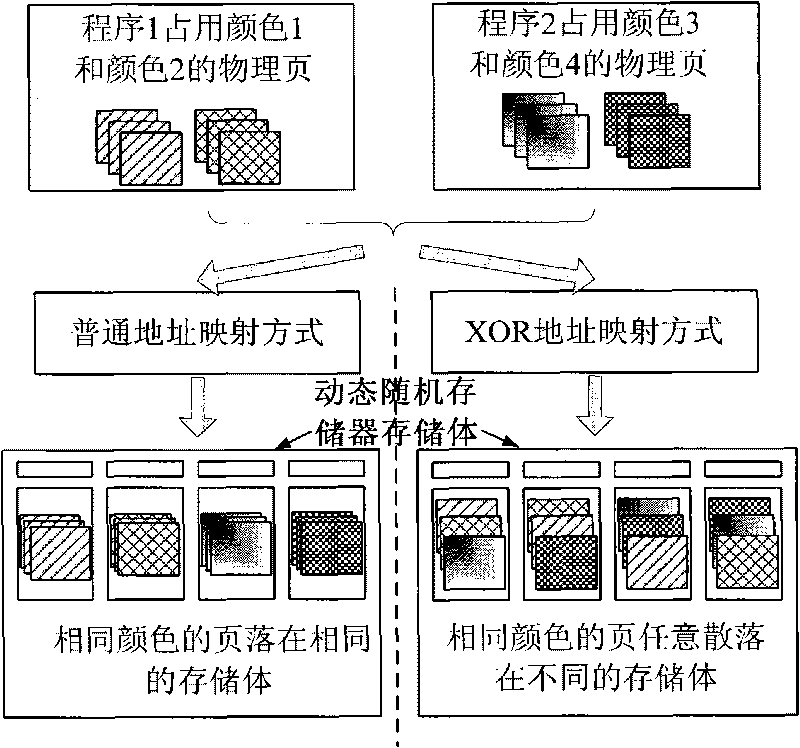

[0074] A method and system for optimizing memory access in a multi-core system of the present invention is an operating system page allocation algorithm based on page coloring, which divides a dynamic random access memory (DRAM) occupied by multiple programs executed simultaneously The bank, try to make different programs occupy different banks, to reduce inter-program line cache conflicts, and then achieve the effect of optimizing memory access speed. The DRAM bank division method based on page coloring proposed in the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More