Chip scale package structure of CMOS (complementary metal-oxide-semiconductor) image sensor and packaging method

A chip-level packaging and image sensor technology, which is applied in the semiconductor field, can solve the problems of a large number of connecting wires, affecting the freedom of connecting wire layout, and failing to meet device integration, so as to reduce defect dislocations and improve efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 approach

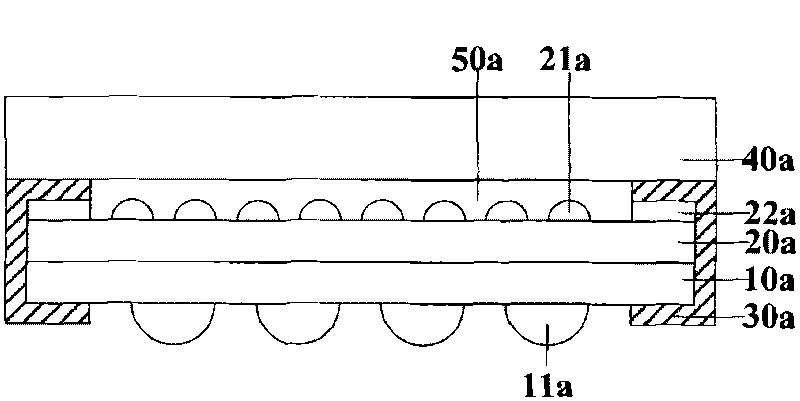

[0016] The first embodiment of the present invention provides a chip-level packaging method for a CMOS semiconductor image sensor, including: providing a semiconductor substrate, forming a photoelectric conversion layer in the semiconductor substrate, and forming a wiring layer on the surface of the photoelectric conversion layer. A discrete connection pad is formed on the surface; an adhesion layer is formed on the surface of the wiring layer, and the adhesion layer covers the connection pad; a support layer is formed on the surface of the adhesion layer; the semiconductor substrate is thinned until the photoelectric conversion layer is exposed, the photoelectric conversion layer An array of pixel elements and a connection layer between the pixel elements are formed thereon, the connection layer is higher than the pixel elements; an adhesive layer is formed on the surface of the microlens layer and the surface of the connection layer; a light-transmitting layer is formed on the ...

no. 2 approach

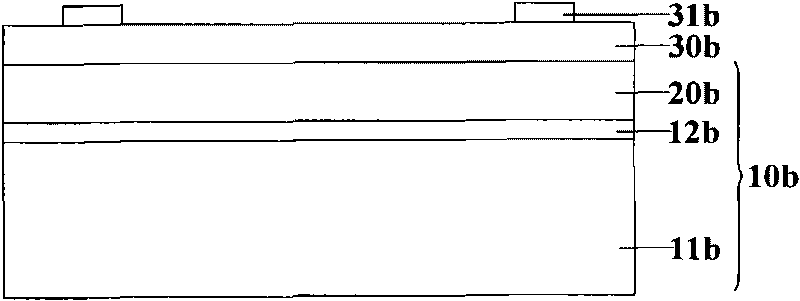

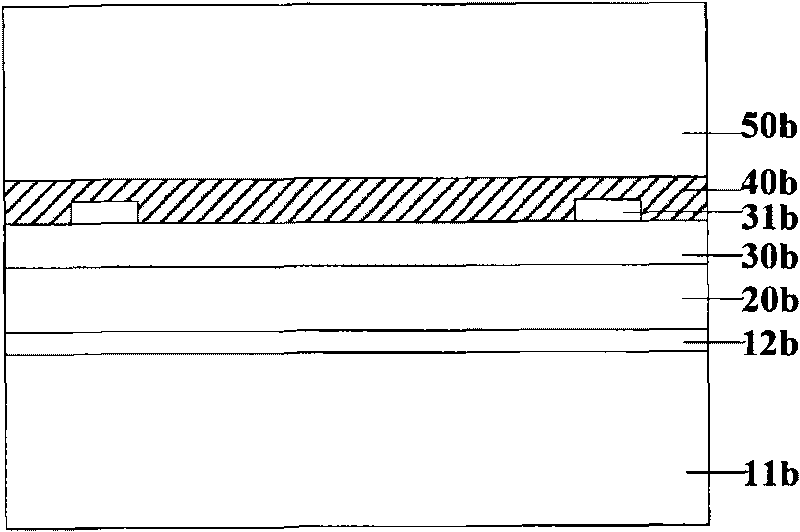

[0040] The first embodiment of the present invention provides a chip-scale packaging method for a CMOS semiconductor image sensor, including providing a semiconductor substrate, forming a photoelectric conversion layer in the semiconductor substrate, and forming a wiring layer on the surface of the photoelectric conversion layer. A discrete connection pad is formed on the surface; an adhesion layer is formed on the surface of the wiring layer, and the adhesion layer covers the connection pad; a support layer is formed on the surface of the adhesion layer; the semiconductor substrate is thinned until the photoelectric conversion layer is exposed, the photoelectric conversion layer An array of pixel elements and a connection layer between the pixel elements are formed thereon, the connection layer is higher than the pixel element; an adhesive layer is formed on the surface of the pixel element and the surface of the connection layer; a light-transmitting layer is formed on the surf...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More