On-wafer self-test and self-repair method

A self-repair and self-test technology, which is applied in the field of integrated circuit testing and integrated circuit design, can solve problems such as increased cost, self-test, and self-repair unit complexity, so as to improve yield and reliability, reduce test cost, and shorten test the effect of time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

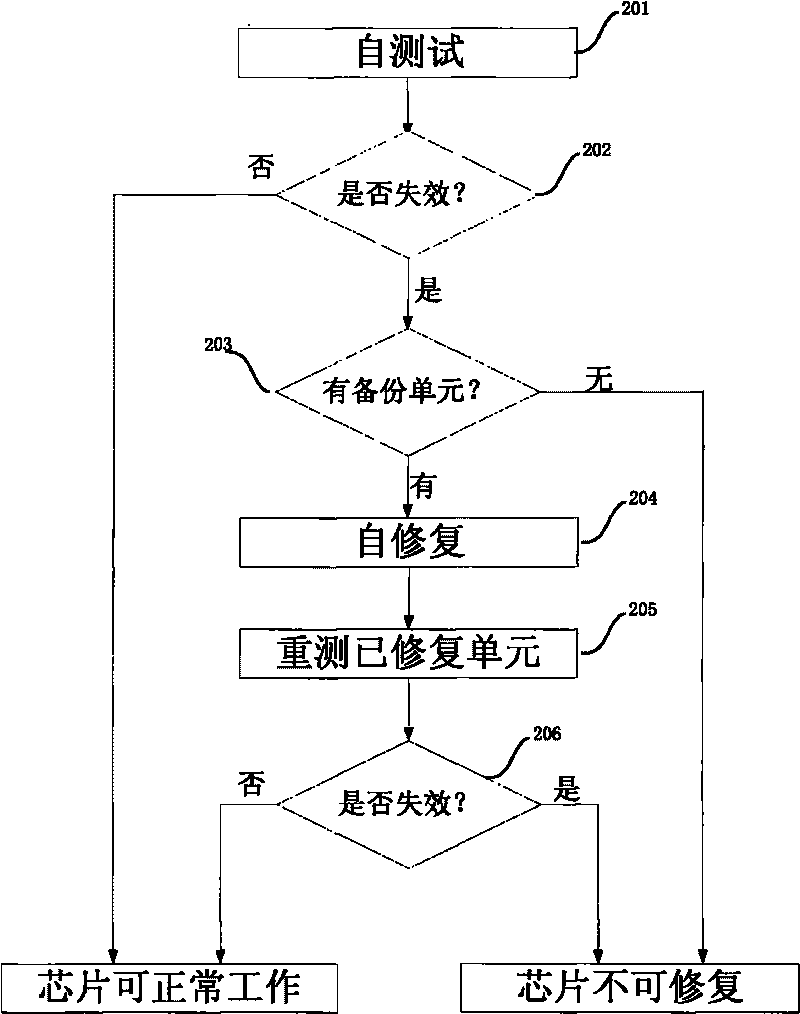

[0055] The technical idea of the invention is to realize the detection and self-repair of the tested unit through the self-test unit and the self-repair unit. Firstly, the self-test unit is used to test whether the unit under test fails, and the test result is passed to the self-repair unit. The self-repair unit uses the backup unit column to replace the failed unit to complete self-repair. Restoration does not require external intervention and complex algorithms.

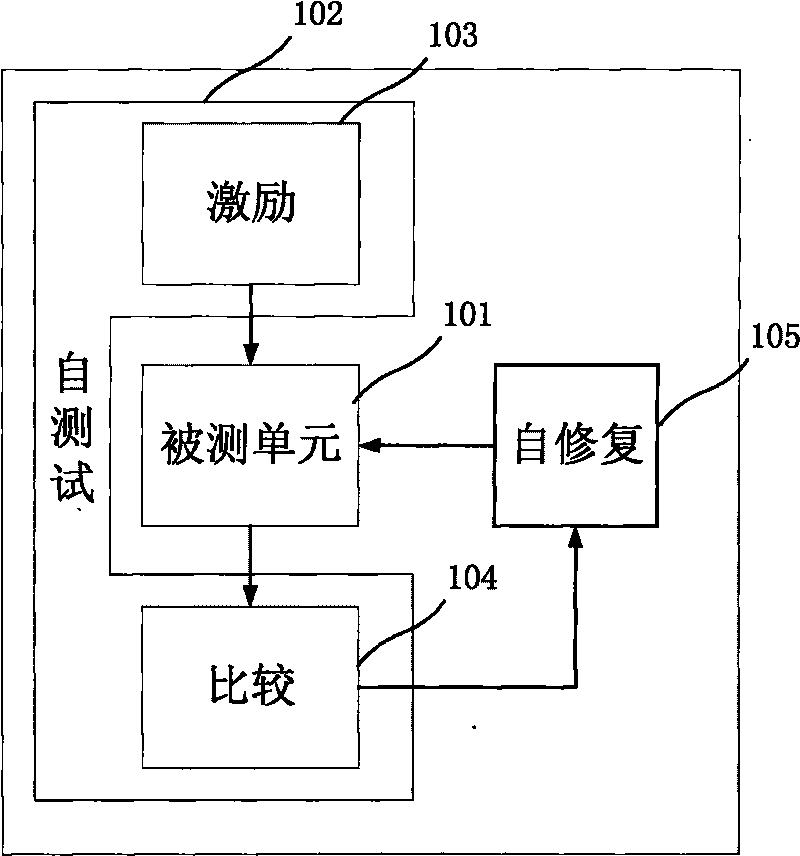

[0056] see figure 1 , which is a structural diagram of a chip system implementing on-chip self-test and self-repair. The system consists of three parts: a unit under test (101), a self-test unit (102) and a self-repair unit (105). Wherein, the tested unit (101) includes but not limited to logic unit, memory, internal wiring, input and output pins. The self-test unit (102) gives the unit under test (101) an incentive (103), and the output of the unit under test is returned to the self-test unit (102) for compar...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More