Semiconductor high-voltage device chip and manufacture method thereof

A high-voltage device and semiconductor technology, applied in the field of semiconductor high-voltage device chips, can solve the problems of increasing grooves, limiting the depth of grooves, and long diffusion time of diffusion temperature, so as to improve heat dissipation capacity, increase breakdown voltage, and reduce the difficulty of scribing Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

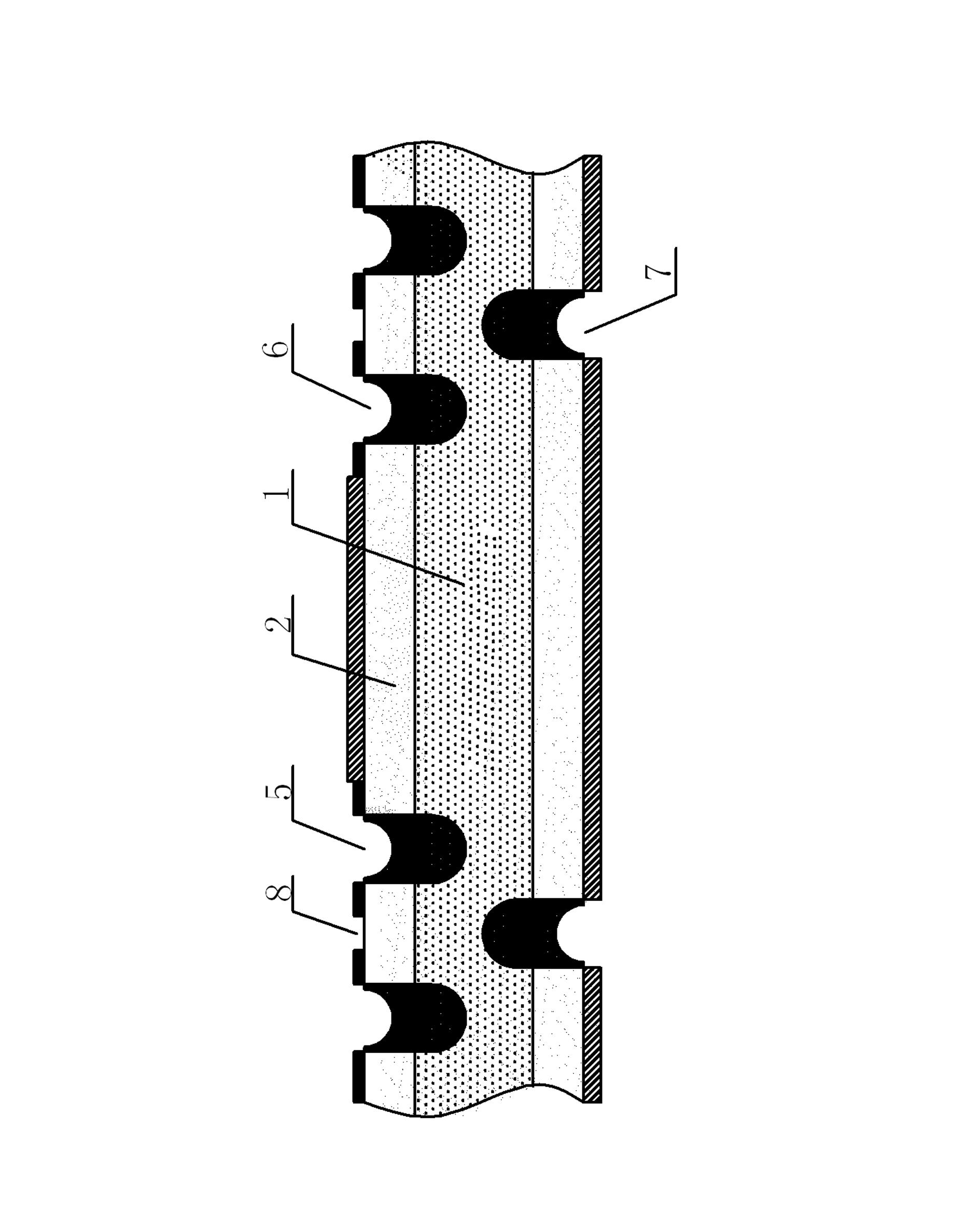

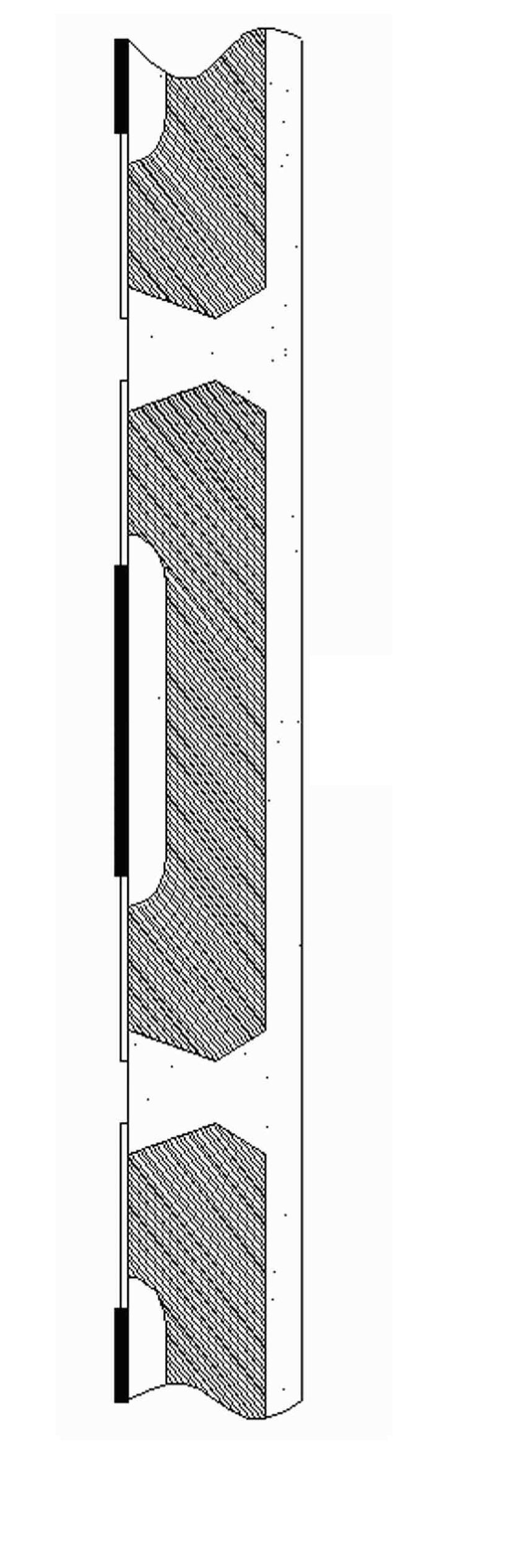

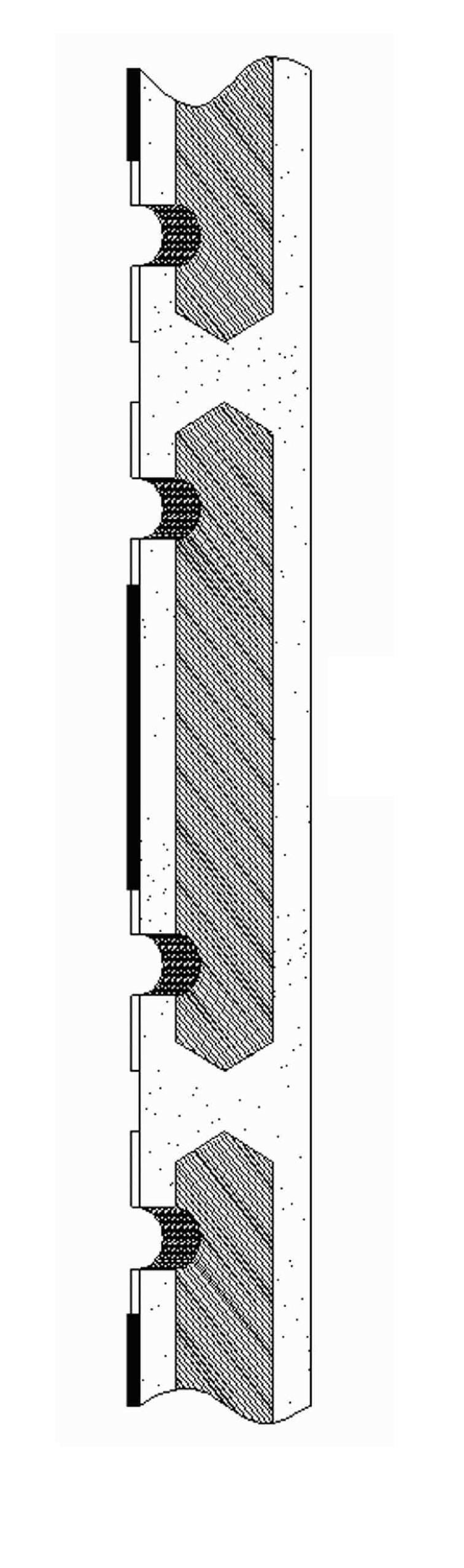

[0027] Such as Figures 4 to 6 As shown, the semiconductor high-voltage device chip includes a silicon single wafer 1, a front P-type diffusion layer 2 formed in the silicon single wafer 1, a back P-type diffusion layer 3, and a front internal annular groove 6 with a width of 100-400um. The half-width of the outer groove 7 inside the back is 90-260um, the depth of the groove is 80-200um, the inner groove 6 and the outer groove 7 are arranged asymmetrically in the longitudinal direction, and a width of 90mm is left between the chips on the front. - 110um spacer zone 8, the side walls and bottom surfaces of the inner groove 6 and the outer groove 7 are covered with an oxygen-doped semi-insulating polysilicon passivation film 4 with a thickness of 1.3-1.8um, and an oxygen-doped semi-insulating polysilicon passivation film 4 is covered with a glass protective film 5 with a thickness of 40-60um.

[0028] The present invention produces the method for semiconductor high-voltage devi...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Width | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Groove depth | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap