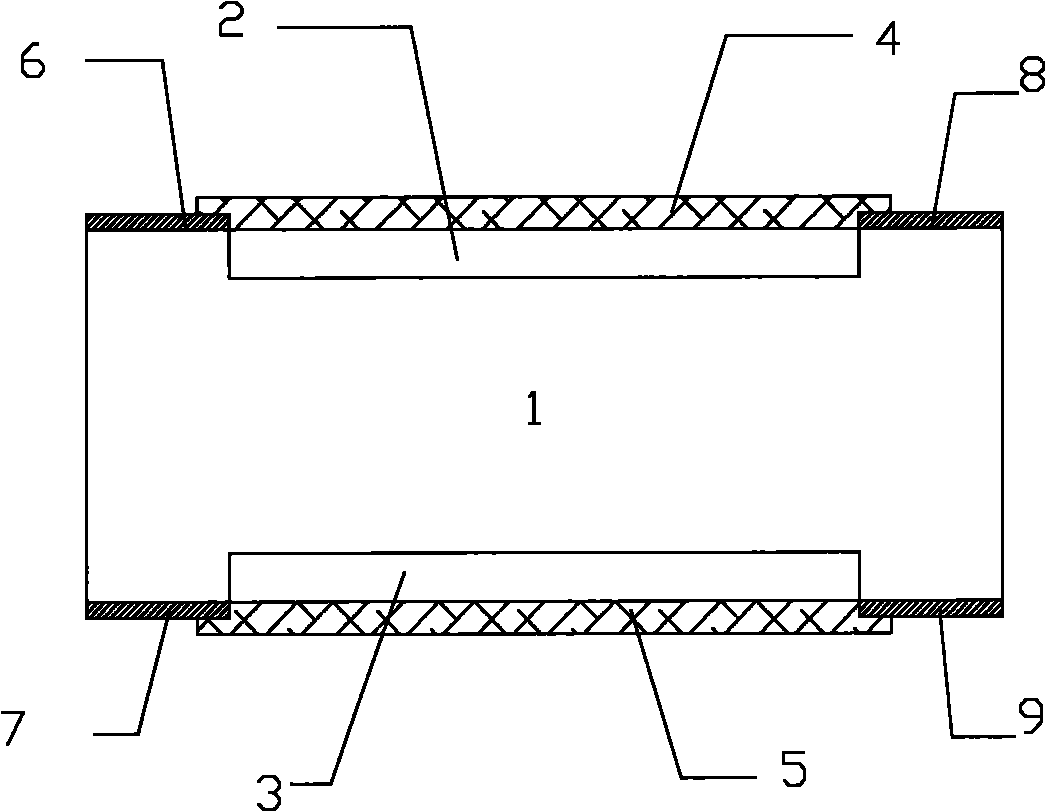

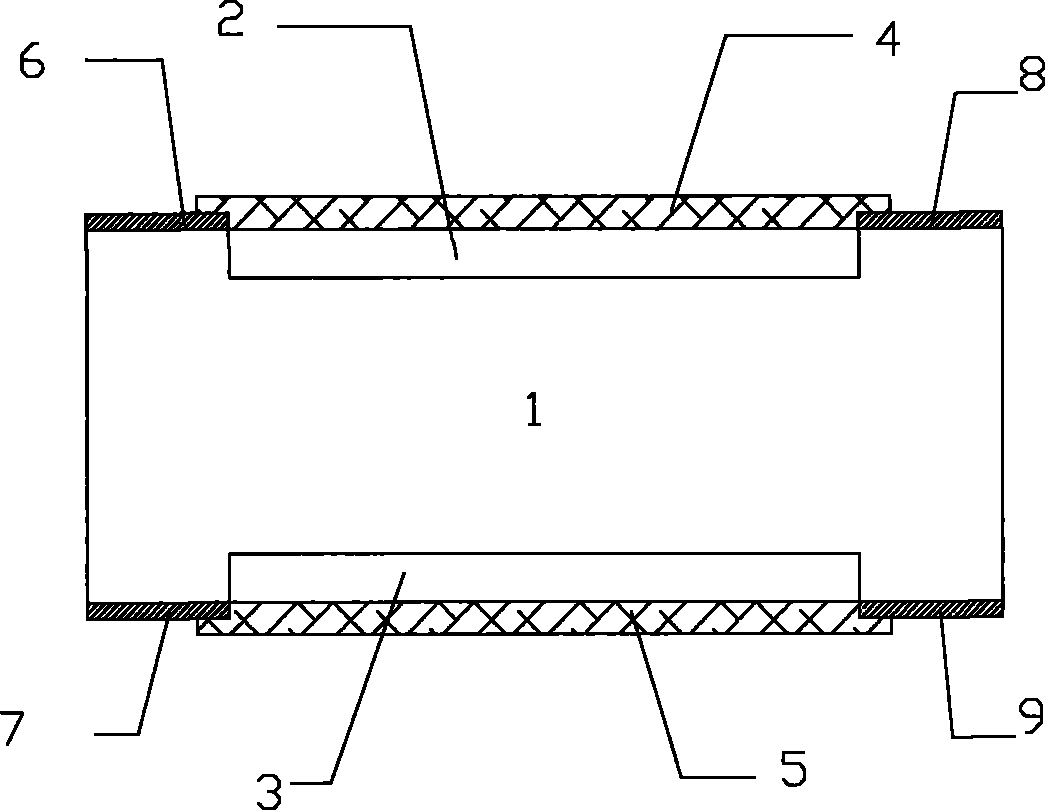

High-power planar junction bidirectional TVS diode chip and production method thereof

A production method and planar junction technology, applied in the direction of electrical components, circuits, semiconductor devices, etc., can solve the problems of reduced product lifetime, low effective utilization rate of silicon wafers, and impact on product reliability, so as to avoid the stress of glass passivation film , short production process and high reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] Select an N-type silicon double-grinding chip with a resistivity of 0.01-0.02Ω.cm and a thickness of 225-235 μm, and produce a high-power planar junction bidirectional TVS diode chip according to the following method:

[0028] 1) Silicon wafer cleaning: Use No. 1 electronic cleaning solution (NH 4 OH:H 2 o 2 :H 2 The volume ratio of O is 1:2:5) and No. 2 electronic cleaning solution (HCL:H 2 o 2 :H 2 The volume ratio of O is 1:2:6) for cleaning, the reaction temperature of the cleaning solution is 85±5°C, the reaction time is 10 minutes, rinse with deionized water (resistivity greater than 14MΩ.cm) for 30 minutes, and dry.

[0029] 2) Oxidation: Put the silicon wafer on the carrier boat, push it into the diffusion furnace, raise the temperature to 1150±5°C, and 2 and O 2 The first oxidation is carried out in the mixed gas composed of 2 、H 2 and O 2 The second oxidation is carried out in the mixed gas, the time is 240±5 minutes, and then in N 2 and O 2 Carry ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More