LDMOS (Lateral Diffused Metal Oxide Semiconductor) manufacturing method

A manufacturing method and ion implantation technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problem of increasing thermal budget, process time and cost, uneven distribution of electric field intensity gradient, and uneven distribution of carrier concentration and other problems, to achieve the effect of saving furnace tube annealing, reducing the risk of surface breakdown, and improving the improvement space

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

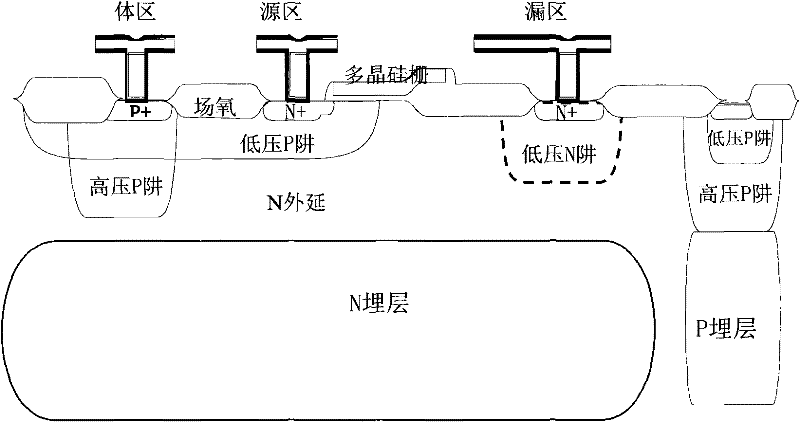

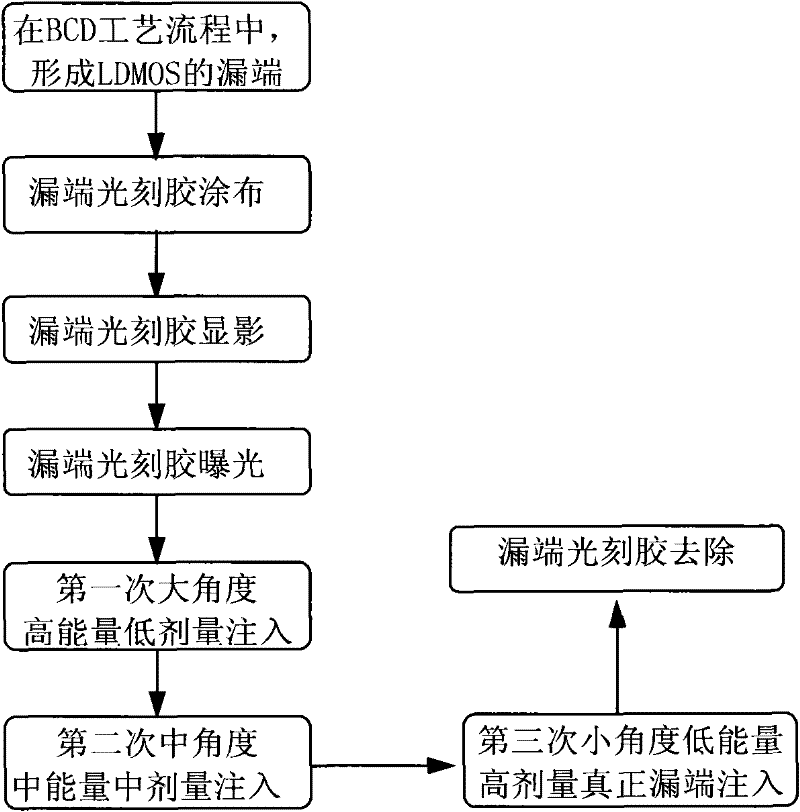

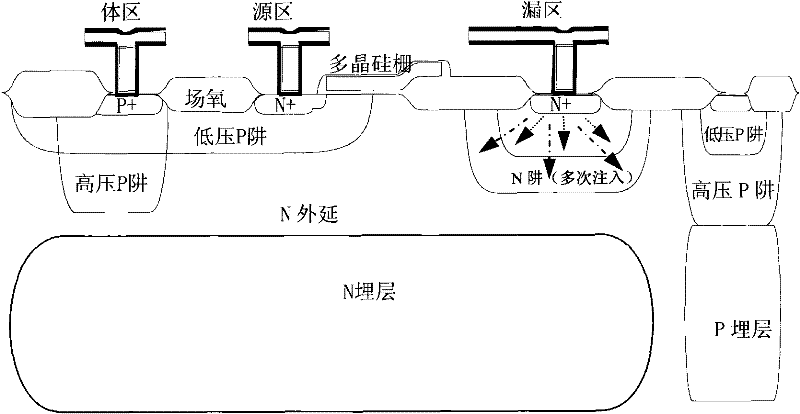

[0015] An embodiment of the LDMOS manufacturing method of the present invention is as follows figure 2 , image 3 As shown, its specific technological process is as follows:

[0016] 1. In the BCD process flow, the drain terminal of LDMOS is formed;

[0017] 2. Carry out photoresist coating at the drain end, develop the drain end, and expose the drain end, and perform more than two ion implantations on the drain end. The angle between the implantation direction and the wafer axis is from large to small, for example, from 45 degrees to 15 degrees, The energy of implanted ions is from high to low, for example, from 1500 kV to 70 kV, and the dose of implanted ions is from low to high, for example, from 1E14 to 1E16. Phosphorus ions, arsenic ions and antimony ions are implanted into the drain of the N-type lateral double-diffused MOS, and boron ions and boron-fluorine ions are implanted into the drain of the P-type lateral double-diffused MOS.

[0018] A preferred embodiment s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More