Method for manufacturing groove MOSFET (Metal-Oxide -Semiconductor Field Effect Transistor)

A kind of manufacturing method, technology of groove

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

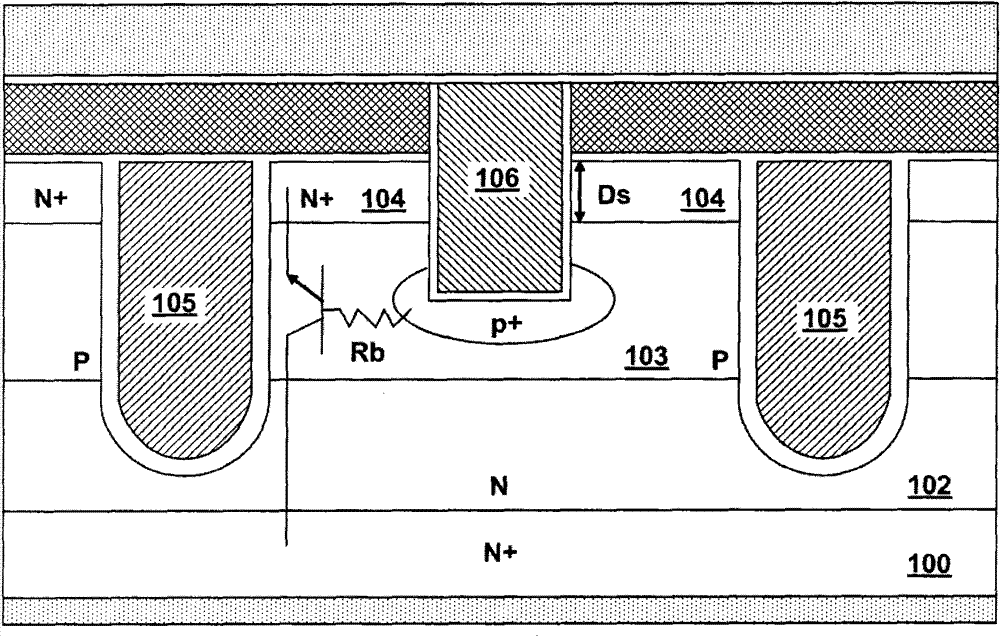

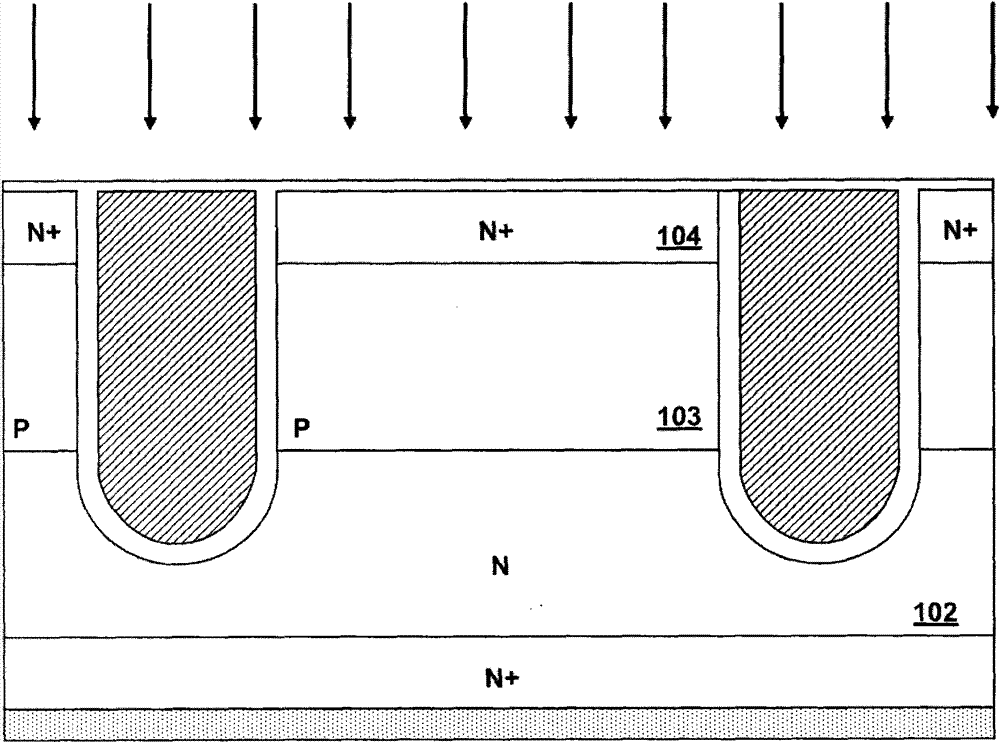

[0065] The invention is explained in more detail below with reference to the accompanying drawings, in which preferred embodiments of the invention are shown. The invention can, however, be embodied in different ways and should not be limited to the embodiments described herein. For example, the description here refers more to N-channel trench MOSFETs, but clearly other devices are possible.

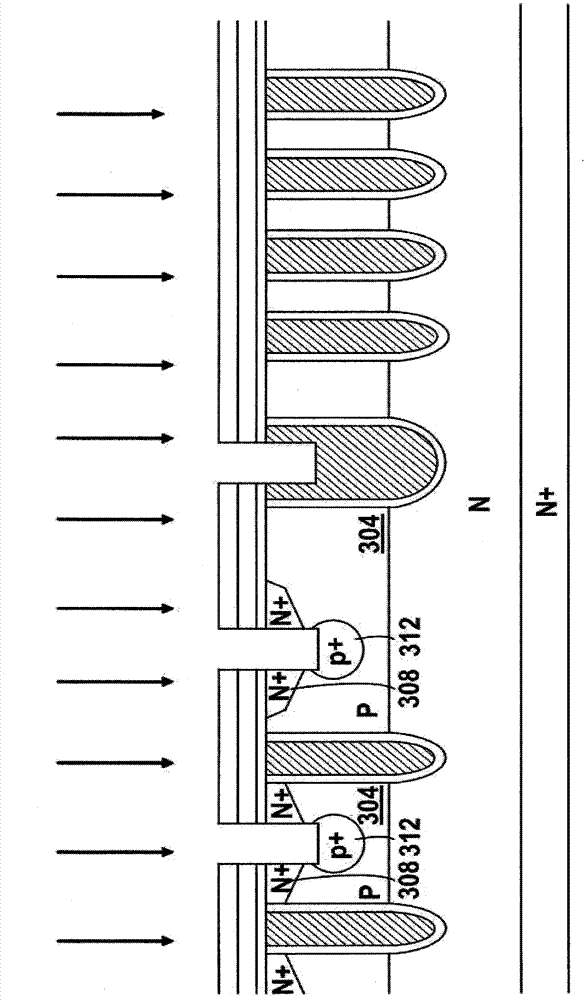

[0066] refer to Figure 3A A preferred embodiment of the invention is shown. The figure also shows Figure 2B or Figure 2C X of top view shown 1 -X 1 ’ sectional view. In the trench MOSFET according to this preferred embodiment, an N-type epitaxial layer 301 is formed on an N+ substrate 300, and a trench formed in the epitaxial layer is lined with a gate oxide 320 and filled with doped polysilicon Trench gates 311 are formed. The P-type body region 304 is formed in the epitaxial layer and is located between every two adjacent trench gates.

[0067] The N+ type source region 308 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More