Optical fiber interface multi-axis motion control system based on FPGA (field programmable gata array) uniprocessor

A fiber optic interface and multi-axis motion technology, applied in the system field of motor control technology, can solve problems such as inability to feed back signals, high expansion costs, and complicated cable layout, and achieve simple hardware, easy development and maintenance, and reduced size Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018]The embodiments of the present invention are described in detail below. This embodiment is implemented on the premise of the technical solution of the present invention, and detailed implementation methods and specific operating procedures are provided, but the protection scope of the present invention is not limited to the following implementation example.

[0019] In this example, the PCI bus is used as the computer bus example, and the IEEE 1394 bus is used as the field bus example, but the protection scope of the present invention is not limited to the described embodiments.

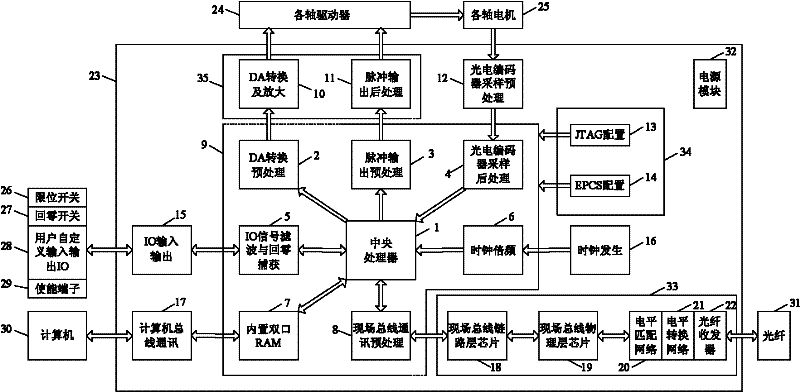

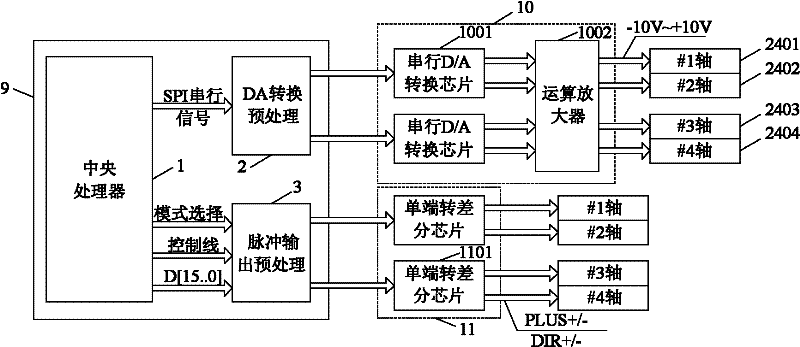

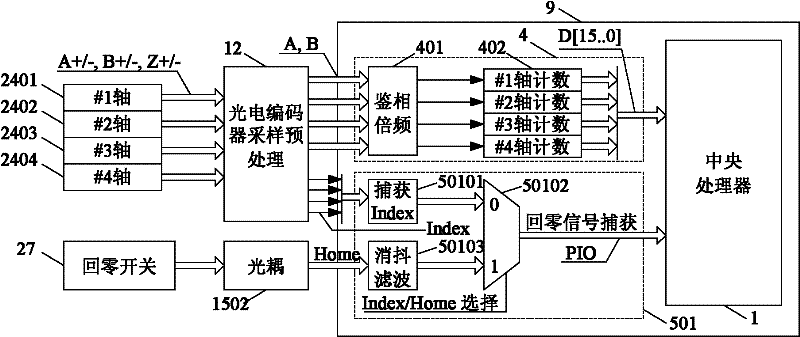

[0020] Such as figure 1 As shown, the present embodiment includes: FPGA control module 9, PCI communication module 17, IEEE 1394 field bus optical fiber communication module 33, D / A conversion amplification 10 and pulse output post-processing module 11, photoelectric encoder sampling pre-processing module 12, IO input and output module 15, power supply module 32, clock generation module 16, FP...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More