Manufacturing method of oxide layer between splitting grids

A manufacturing method and gate oxide layer technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as thick oxide layer, inability to meet process requirements, serious smile effect, etc., achieve short process time, improve Smile effect, avoiding the effect of excessively thick oxide layer

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

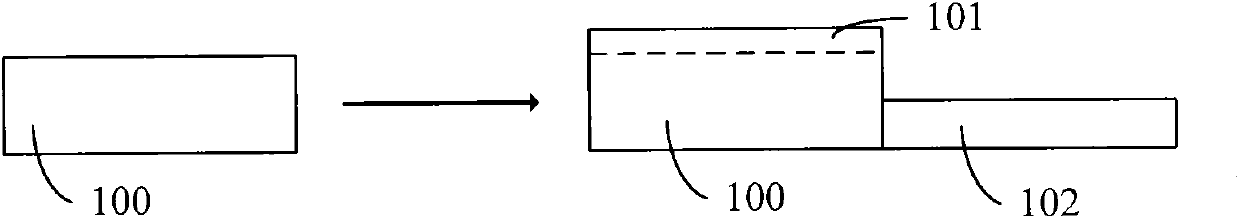

[0016] For this reason, the manufacturing method of the oxide layer between the split gates of the present invention adopts a rapid thermal process to grow the oxide layer in the ion implantation region. According to an embodiment of the present invention, it includes: using rapid thermal process (RTP, Rapid Thermal Process) equipment to perform in-situ steam generation (ISSG, In-Situ Steam Generation), so that the surface of the common source region between the split gates form an oxide layer.

[0017] The method of in-situ water vapor generation grows an oxide layer through a high-temperature water vapor atmosphere, and the growth rate of the oxide layer is relatively fast. Moreover, the rapid thermal process equipment has a fast heating and cooling speed. At the same time, the rapid thermal process equipment is a single-wafer process equipment. Compared with the situation where the furnace tube oxidation is usually dozens of wafers, the gas source that the wafers in the rap...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More