Method for extracting gate-oxide thickness and substrate doping concentration of field effect transistor

A gate oxide layer thickness, field effect transistor technology, applied in the field of extracting field effect transistor gate oxide layer thickness and substrate doping concentration, can solve the problem of reducing the accuracy of parameters, and achieve the effect of simple structure and high accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

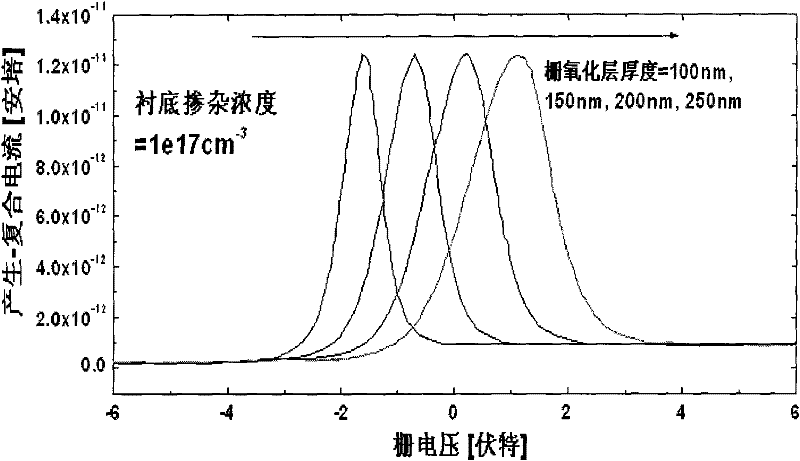

[0022] The specific process of using the forward gate-controlled diode to generate-recombined current to extract the gate oxide layer thickness and substrate doping concentration of the SOI field effect transistor is given below:

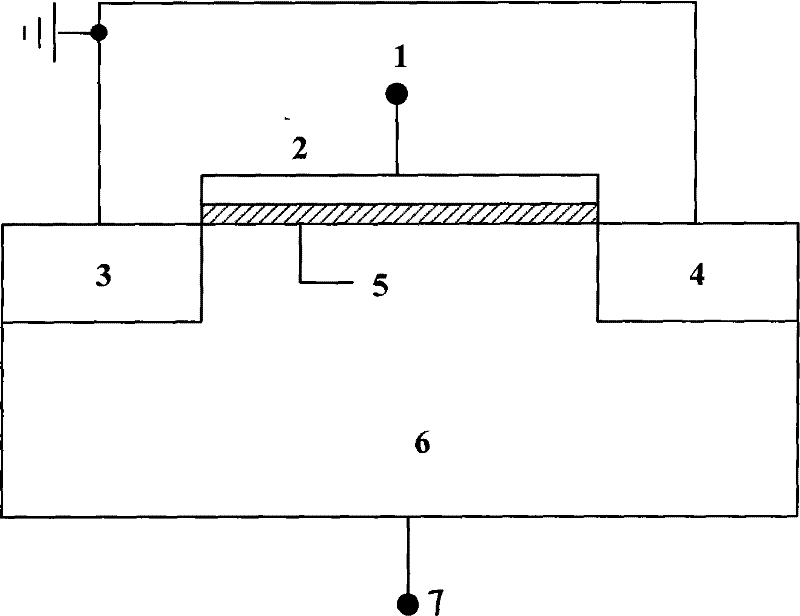

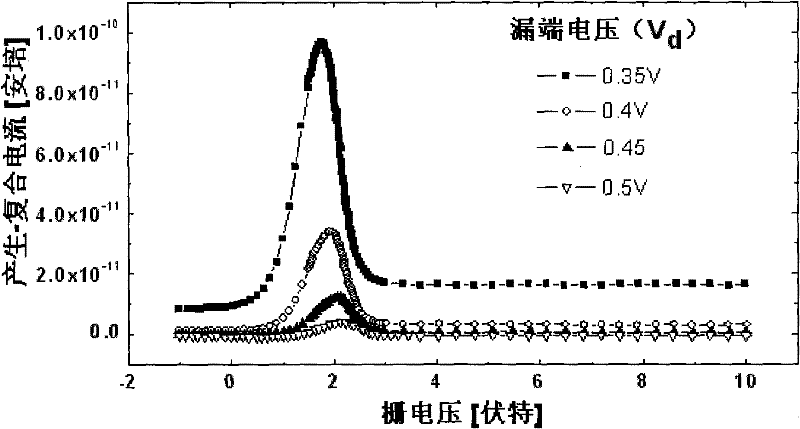

[0023] 1) Ground the source and drain of the SOI field effect transistor, and set the substrate bias voltage to 0.35V, 0.4V, 0.45V and 0.5V respectively, so that the drain-substrate diode is forward biased but not conducting. The test structure diagram is as follows figure 1 Shown; Among them, 1 is the gate voltage, 2 is the gate, 3 is the source, 4 is the drain, 5 is the oxide layer, 6 is the substrate, and 7 is the substrate voltage.

[0024] 2) The gate voltage is swept from -0.5V to +0.5V, and the voltage range includes the gate voltage corresponding to the peak value of the generation-recombination current. Measure the generation-recombination current at the drain, and obtain the relationship curve between generation-recombination current and g...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More