Transverse high-voltage MOS device and manufacturing method thereof

A MOS device and lateral high voltage technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of device damage, reduced device performance, high dependence, etc., achieve good process stability, reduce surface electric field, The effect of improving the withstand voltage performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

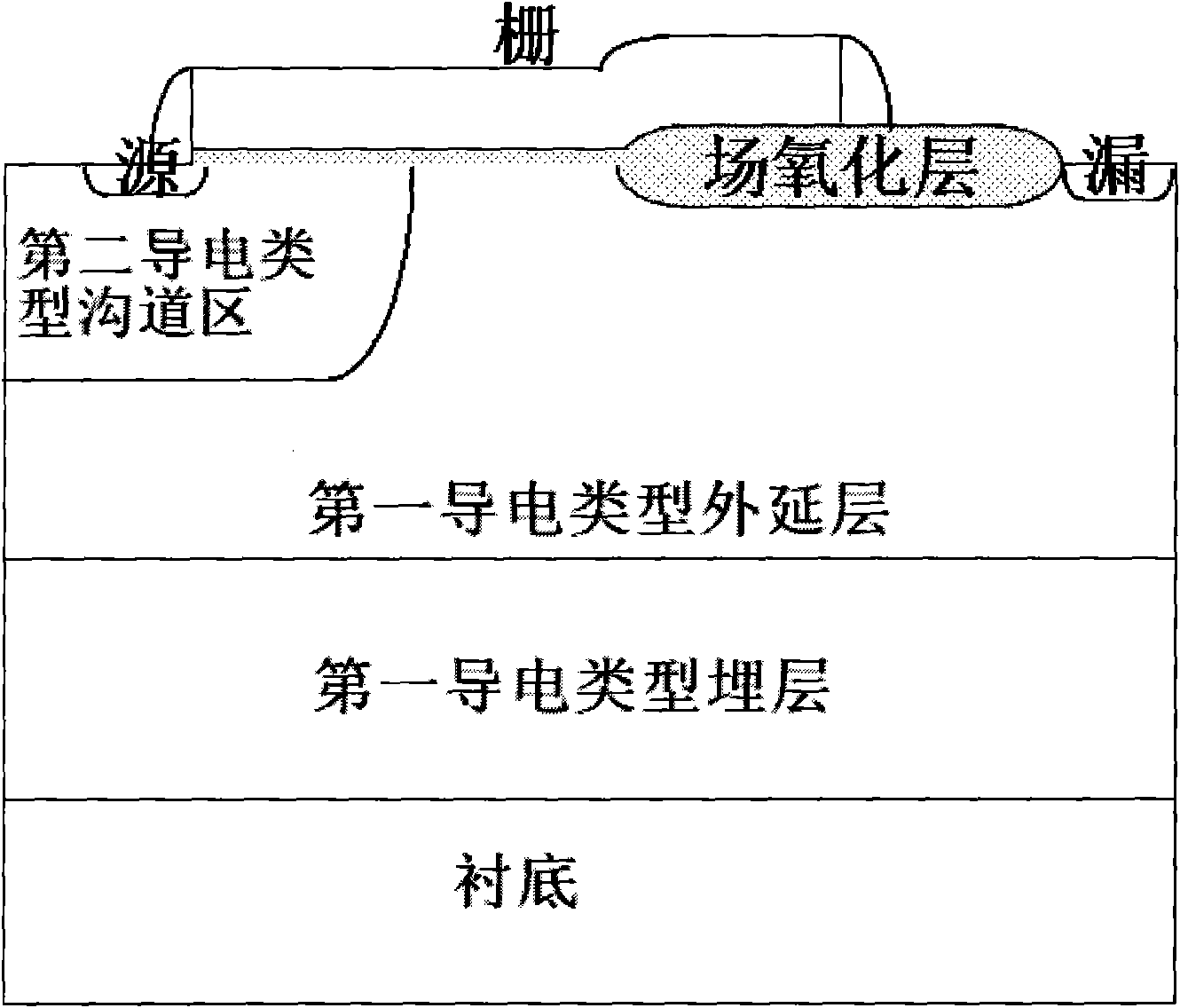

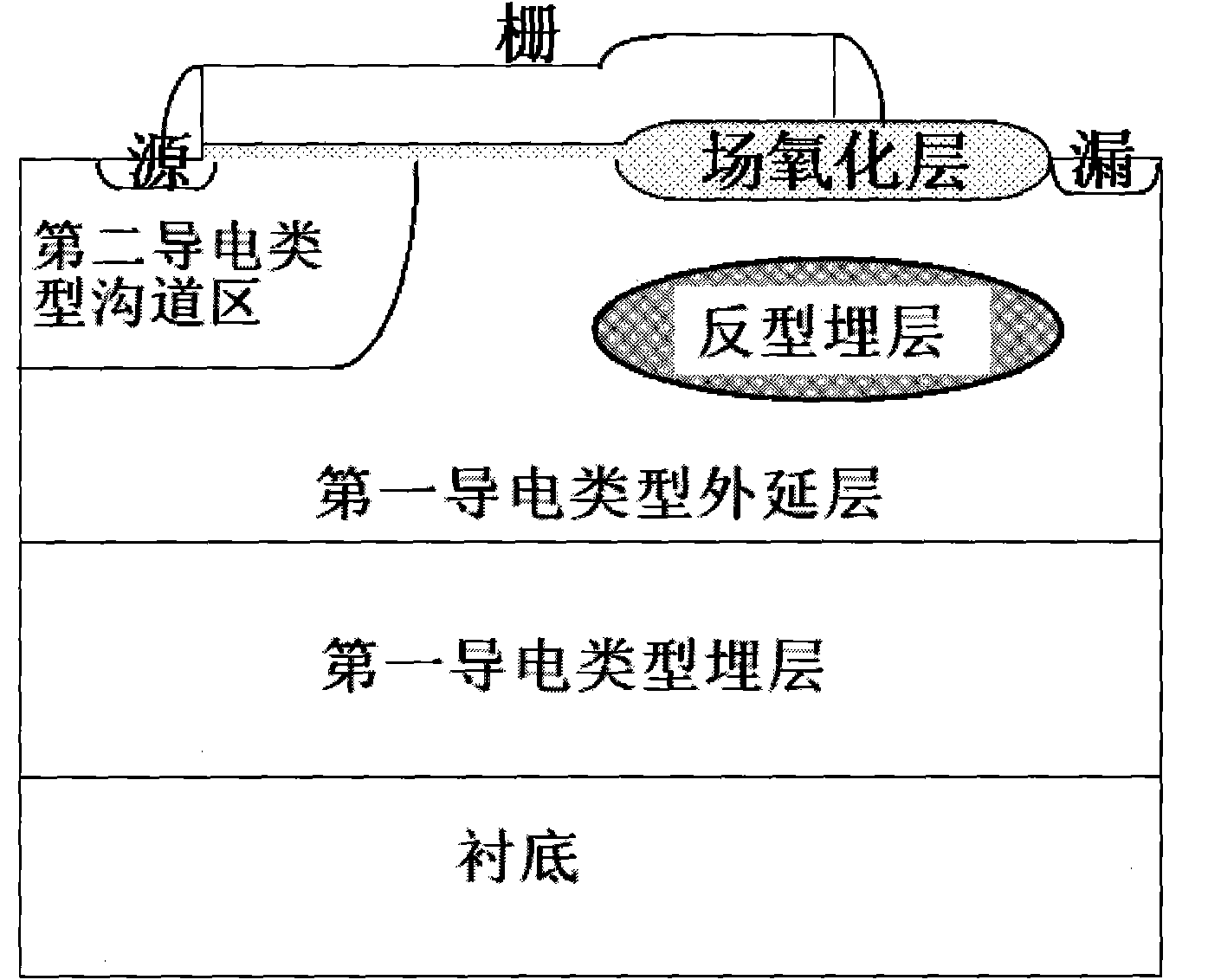

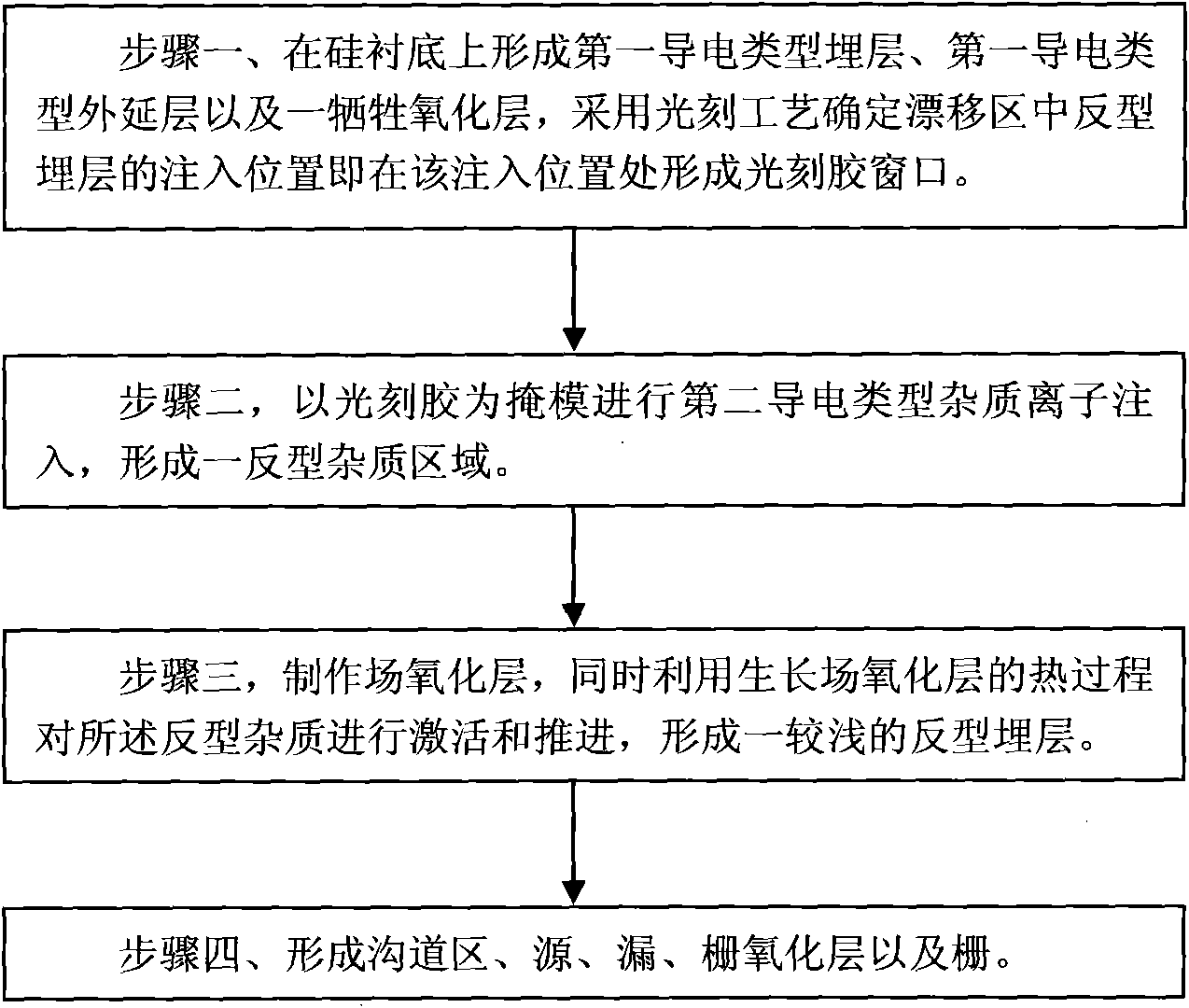

[0023] Such as figure 2 Shown is a schematic structural view of the lateral high voltage MOS device of the present invention. The method includes: forming a first conductivity type buried layer on a silicon substrate, and forming a first conductivity type epitaxial layer on the first conductivity type buried layer; forming a second conductivity type epitaxial layer in the first conductivity type epitaxial layer. type channel region, forming a heavily doped first conductivity type source region in the second conductivity type channel region; forming a heavily doped first conductivity type drain region in the first conductivity type epitaxial layer; The epitaxial layer of the first conductivity type between the channel region and the drain region is used as a drift region of the device; a field oxide layer is formed on the drift region and is connected to the drain region; a gate oxide layer is formed on the channel region, and the gate The oxide layer covers the entire channe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More