Computer based on programmable hardware computing platform

A computing platform and computer technology, applied in electronic science and fields, to achieve the effect of improving parallelism and computing efficiency, avoiding clock domain convergence problems, and reducing work performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

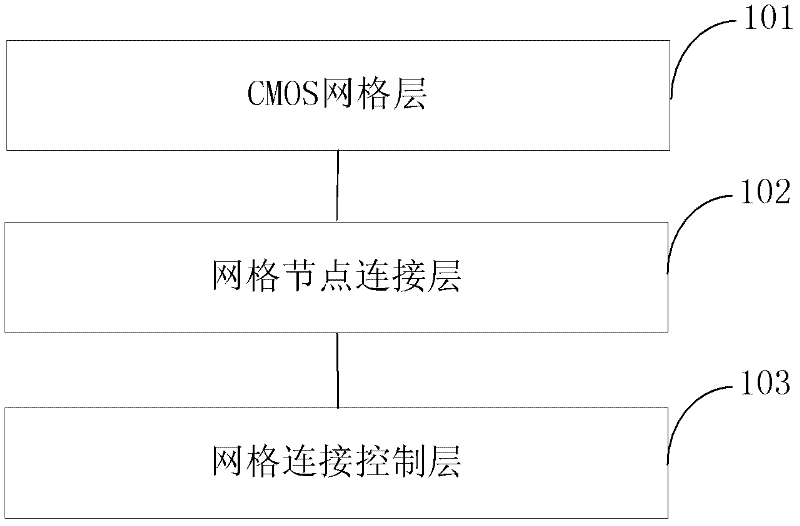

[0048] see figure 1 As shown, it is a schematic structural diagram of a computer based on a programmable hardware computing platform provided in this embodiment, which specifically includes:

[0049] The CMOS grid layer 101 is composed of multiple grid units tiled. Each grid unit includes multiple MOS transistor pairs and multiple connection nodes. Adjacent grid units are connected to each other through shared connection nodes. Each connection The nodes are respectively connected to multiple MOS tube pairs in the grid unit where they are located;

[0050] The grid node connection layer 102 includes a plurality of grid nodes, and each grid node is connected to a connection node in the grid unit, including a plurality of shielding switches and node state switches, and the shielding switch controls the working state of the MOS tube pair, and the node The state switch is used to control the connection state between the MOS tube pairs;

[0051] The grid connection control layer 1...

Embodiment 2

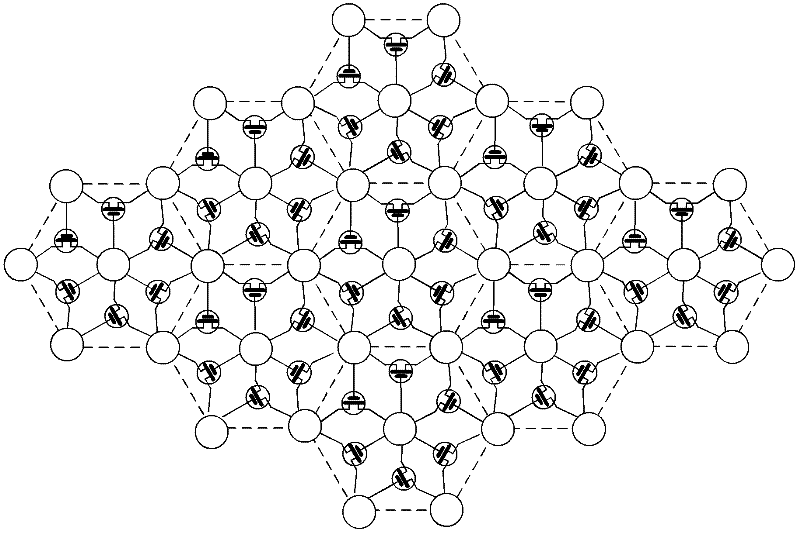

[0059] This embodiment provides a specific structure of the CMOS grid layer described in Embodiment 1, see Figure 2a Shown is a schematic diagram of a specific structure of a CMOS grid layer in a computer based on a programmable hardware computing platform.

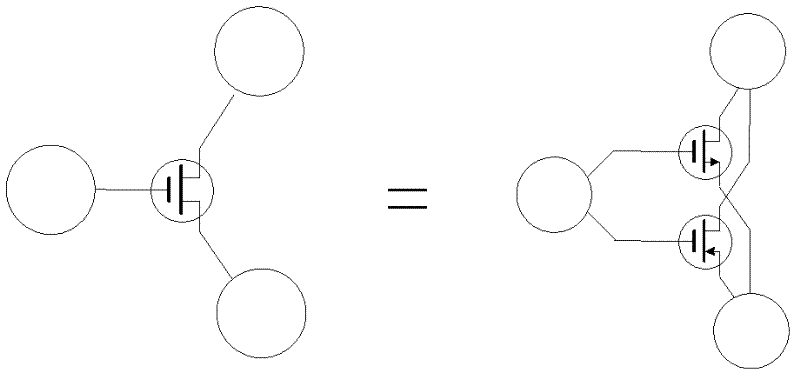

[0060] Wherein the grid unit can be a regular hexagonal structure, and each grid unit includes 6 MOS transistor pairs and multiple connection nodes; each MOS transistor pair includes an NMOS transistor and a PMOS transistor with the same direction; each connection The node includes 12 connection channels, which are respectively connected to 6 MOS tube pairs. As shown in FIG. 2 , the MOS transistors graphically represent pairs of MOS transistors that are composed of NMOS transistors and PMOS transistors in the same direction, and all circles in the figure represent connection nodes. Due to the symmetry of the drain and source of the MOS transistor, the position of the drain and source of each NMOS transistor and PMOS tra...

Embodiment 3

[0074] This embodiment provides a specific structure of the grid node described in Embodiment 1, see Figure 7 As shown, it is a schematic diagram of the serial number of a connection node and the pair of MOS transistors it is connected to. The MOS transistor graphic represents a pair of MOS transistors composed of NMOS transistors and PMOS transistors with the same direction. The circle shown in the graph represents Connect the nodes. see Figure 8 As shown, it is a schematic diagram of the structure of the grid node:

[0075] Wherein: the pins of the two NMOS transistors on the diagonal of each connection node are connected to each other; the pins of the two PMOS transistors are connected to each other.

[0076] Each grid node may include 6 shielding switches, and the gates of the 6 MOS transistors in the 3 MOS transistor pairs are respectively connected to the corresponding shielding switches through the connection nodes;

[0077] The shielding switch is used to separate...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More