Method for testing reliability of semiconductor devices

A semiconductor and reliability technology, applied in the field of non-destructive rapid testing of pMOSFET negative bias temperature instability, can solve problems such as time-consuming workload of NBTI testing, degradation of electrical parameters of device samples, and inability to continue to use, etc. Achieve the effect of reducing test time, significant efficiency, and improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

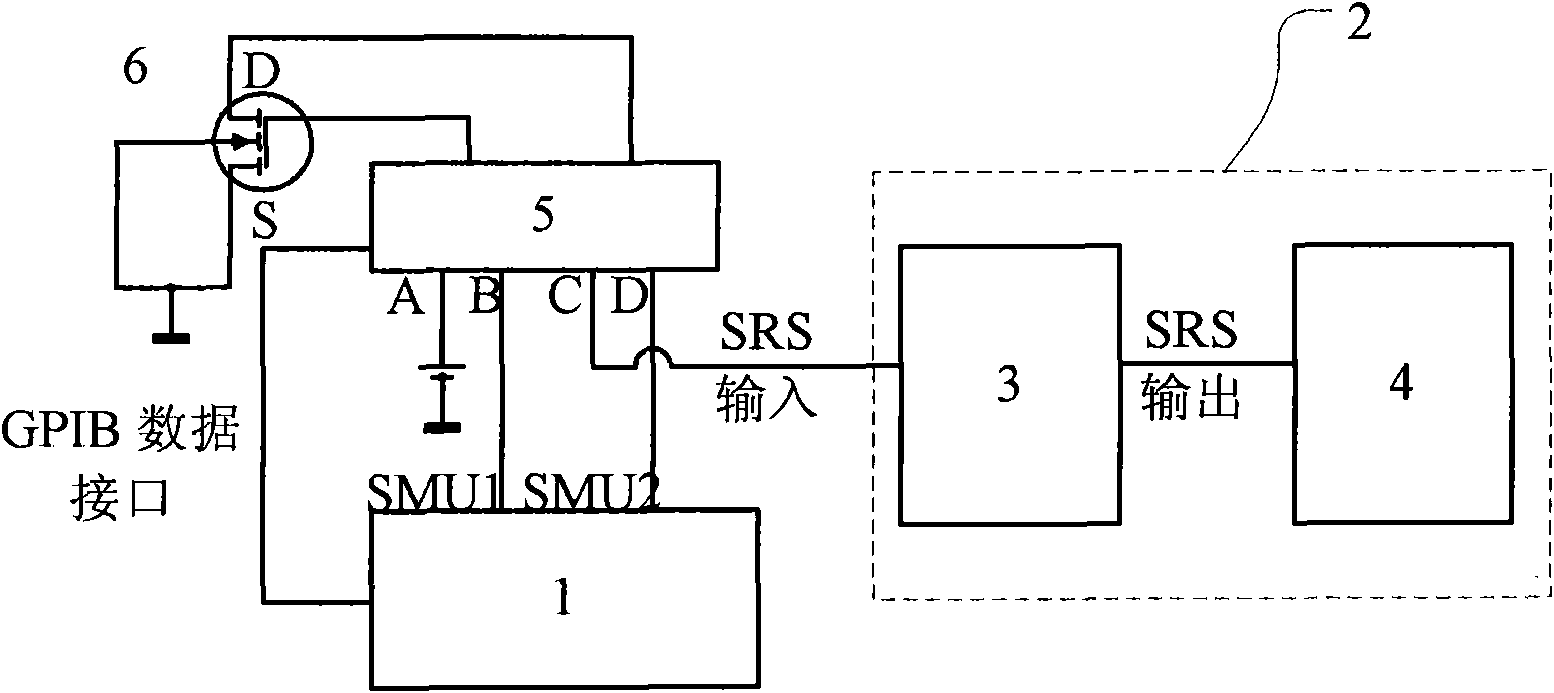

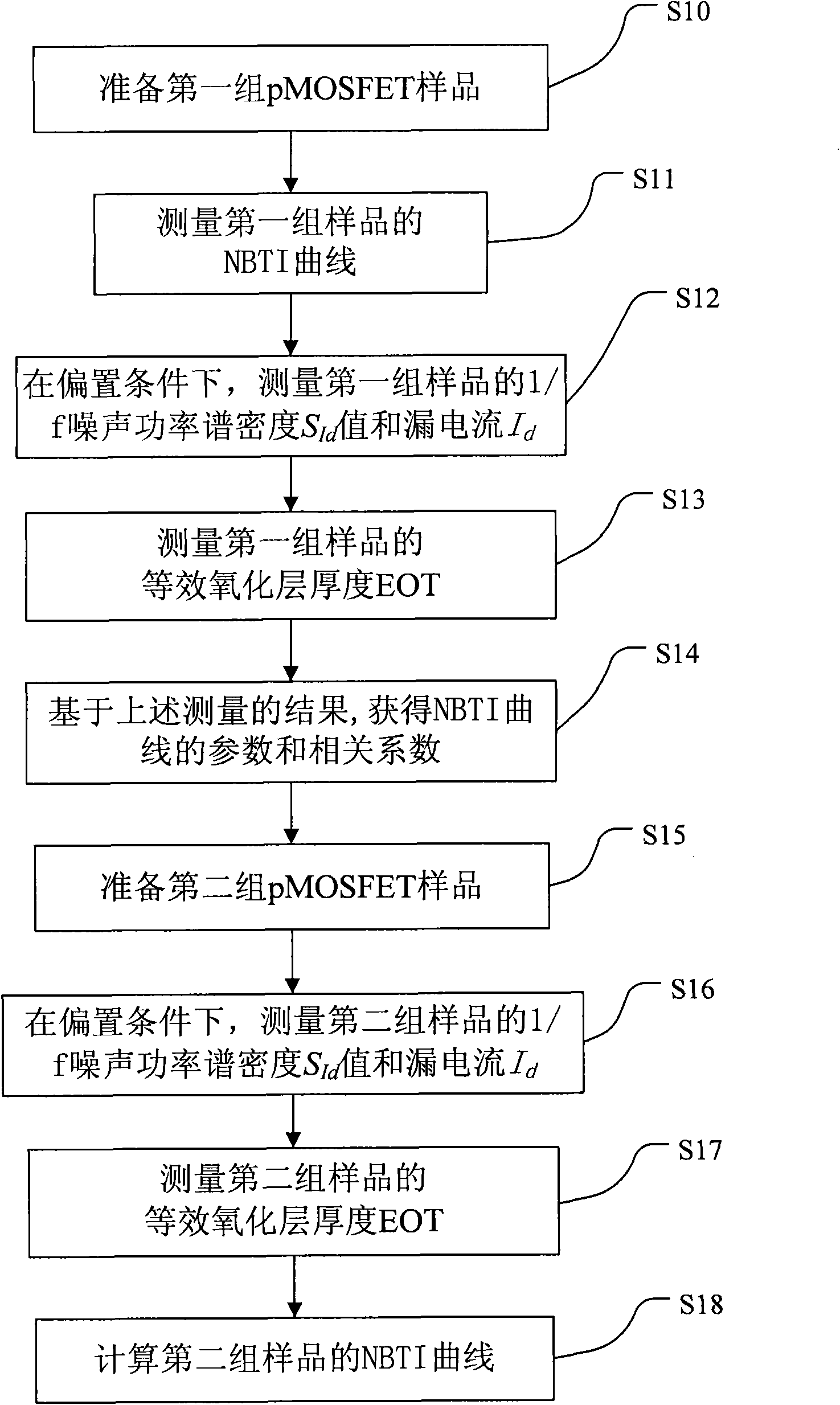

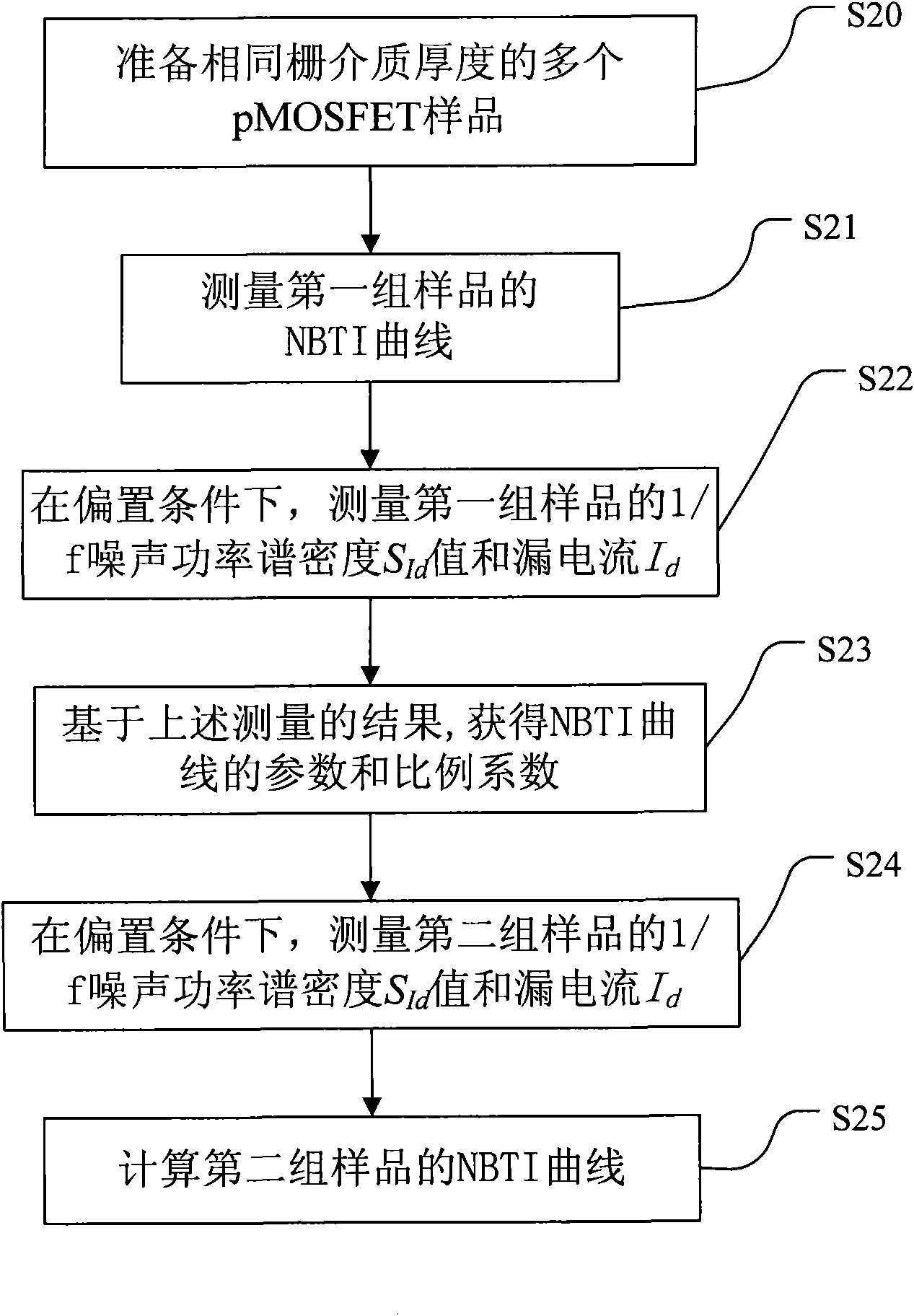

[0019] The inventor found and established the initial stage V of the NBTI curve of pMOSFET th The correlation between the degradation value and the amplitude of the power spectral density of 1 / f noise, and based on this, a new method for testing the reliability of semiconductor devices is proposed.

[0020] Research on the NBTI mechanism has been going on for more than 40 years. At present, it is generally believed that the physical mechanism of NBTI is the interface state N it And filled near-interface bulk charge trap N t The combined effect of For the generation of the interface state, the more recognized reaction-diffusion model and its modified model believe that the fracture reaction of the Si-H bond at the interface and the subsequent dimerization and diffusion of H particles in the dielectric layer work together to cause the threshold voltage to drift. The index changes with time; since the interface reaction and dimerization are rapid, the subsequent degradation will be ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More