SOI (silicon on insulator) LIGBT (lateral insulated gate bipolar transistor) device unit with p buried layer and longitudinal channel

A channel and device technology, applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve the problems of limiting the lateral withstand voltage of the device, deteriorating the thermal characteristics of the device, and aggravating the self-heating effect, so as to increase the vertical withstand voltage and improve the modulation effect , the effect of eliminating adverse effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

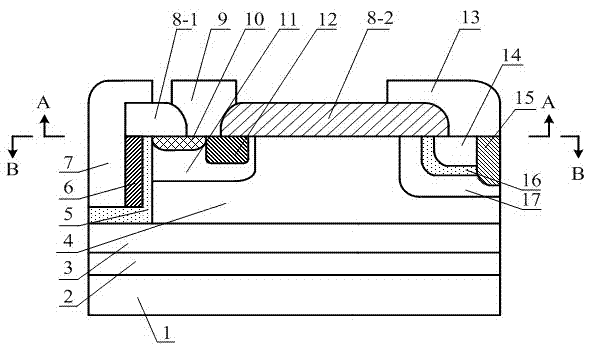

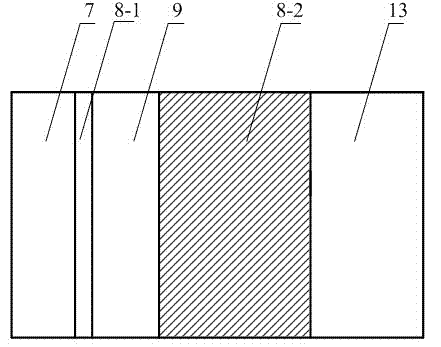

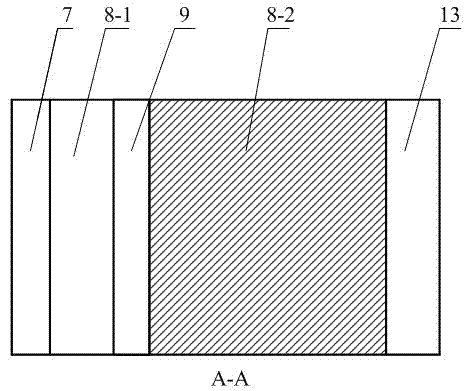

[0013] Such as figure 1 , 2 , 3 and 4, a vertical channel SOI LIGBT device unit with a p-buried layer, including a p-type semiconductor substrate 1, a buried oxide layer 2, a p-buried layer region 3, and an n-type lightly doped drift region 4 , a gate oxide layer 5, a buried oxide layer 2 covering the p-type semiconductor substrate 1, a p-buried layer region 3 covering the buried oxide layer 2, an n-type lightly doped drift region 4 and a gate oxide layer 5 arranged side by side On the p buried layer region 3, the n-type lightly doped drift region 4 is in contact with the gate oxide layer 5, and the n-type heavily doped polysilicon gate 6 is arranged next to the gate oxide layer 5, and one side of the n-type heavily doped polysilicon gate 6 It is in contact with one side of the gate oxide layer 5 .

[0014] A first p-type well region 11 and an n-type buffer region 17 are respectively embedded on both sides of the top of the n-type lightly doped drift region 4, wherein the fi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More