STI (Shallow Trench Isolation) structure and manufacturing method thereof

A trench isolation and trench technology, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of reduced trench isolation function, short circuit of semiconductor devices, high sensitivity of trench 20 shape, and achieve isolation performance Good, enlarged aspect ratio effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

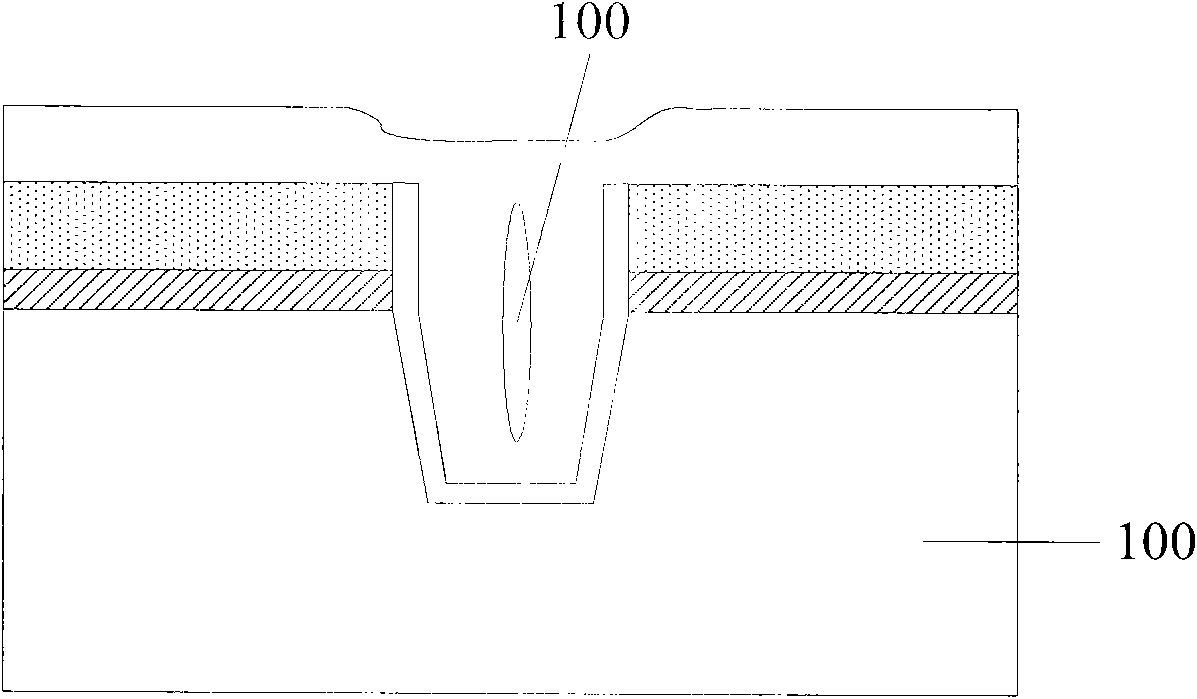

Image

Examples

Embodiment Construction

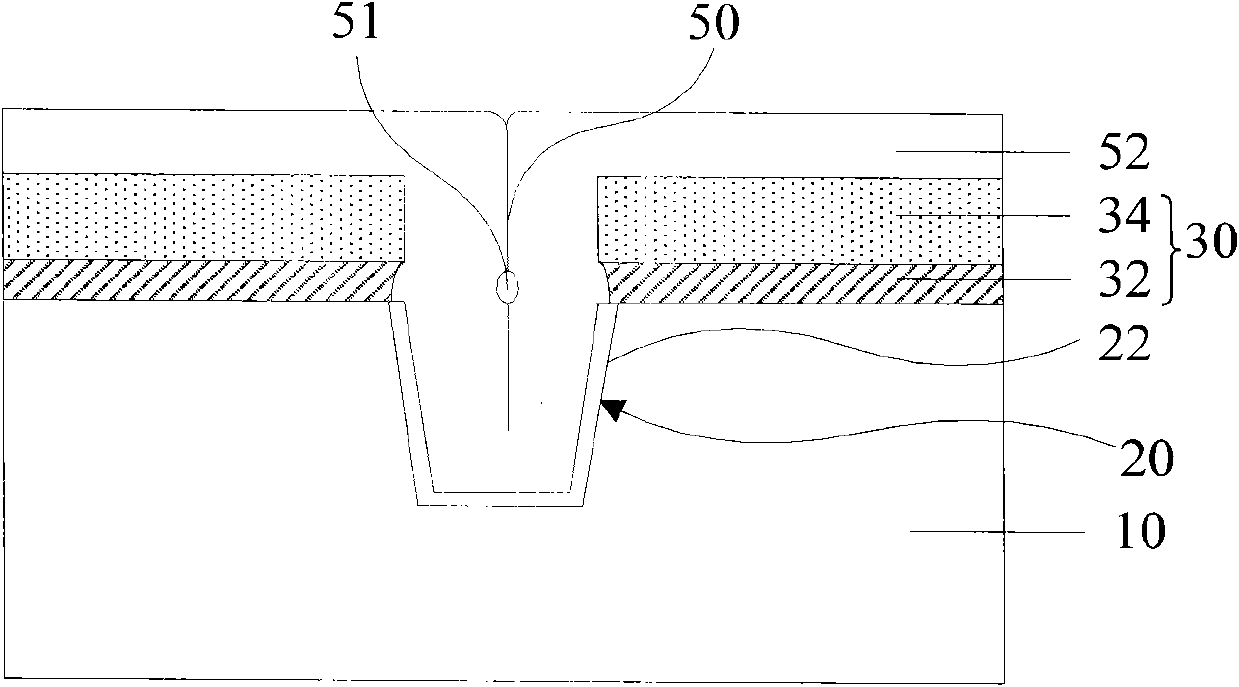

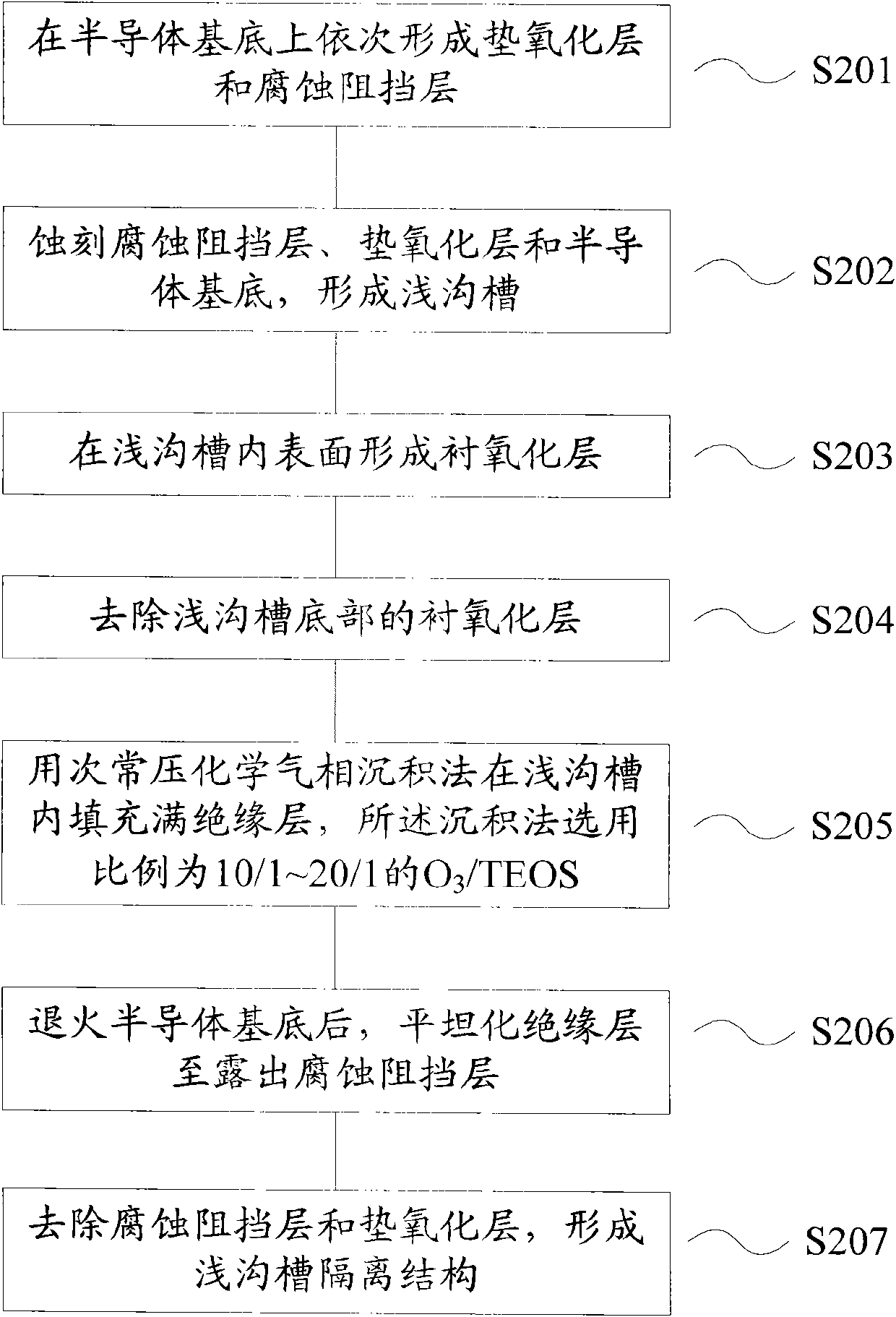

[0024] The core of the present invention is to first deposit the first insulating layer to fill the trenches by sub-atmospheric pressure chemical vapor deposition, and then remove part of the first insulating layer that is prone to gap defects, and then use wet etching to remove part of the liner nitride layer Make it the same depth as the first insulating layer, and finally deposit the second insulating layer to fill the trench. Using the method, the complete filling of the bottom of the trench with high aspect ratio is realized, and during the process of depositing the second insulating layer, Since the depth of the trench is reduced and the width is increased (part of the liner nitride layer is removed from the sidewall of the trench), filling of the trench is easier to implement and avoids the defects of possible gaps in the prior art.

[0025] The specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings. ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More