Manufacturing method of shallow trench isolation

A manufacturing method and technology of shallow trenches, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of high cost, low cost-efficiency ratio, and complicated process steps, so as to reduce process cost and realize smoothness The effect of simplifying and simplifying the process steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

[0039] Figure 8 to Figure 15 It is a process schematic diagram of the first embodiment of the method of the present invention. The manufacturing method of this embodiment will be described in detail in conjunction with the accompanying drawings.

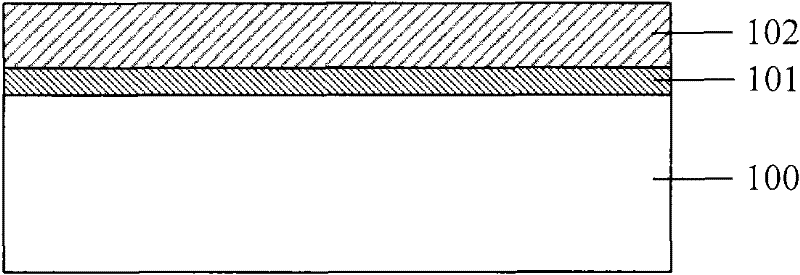

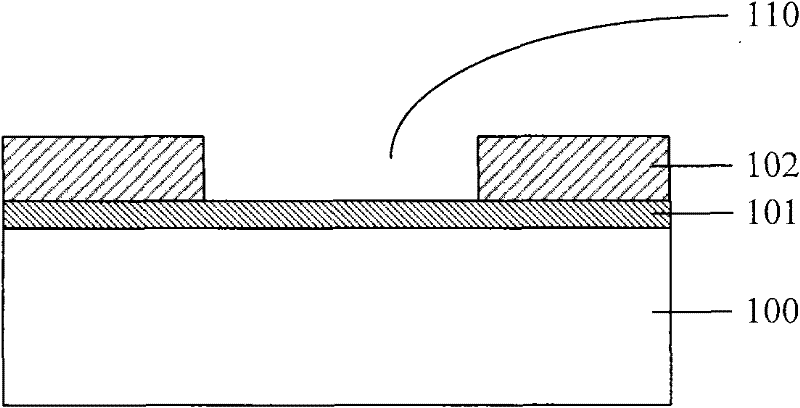

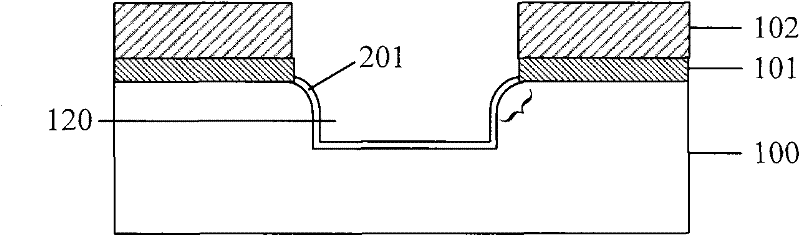

[0040] Such as Figure 8As shown, firstly, a semiconductor substrate 300 is provided, and the semiconductor substrate 300 is covered with a mask structure 301 . The mask structure 301 may be a single layer of silicon oxide layer, silicon nitride layer or polysilicon layer or a stack structure of any combination, and may also be a stack structure of a dielectric layer and a mask layer stacked in sequence. When the dielectric layer is used to form openings in the photolithography mask structure 301 , it plays the role of etching stop and protecting the semiconductor substrate 300 . The thickness of the mask structure 301 may be 100 nm to 120 nm. In this embodiment, the semiconductor substrate 300 is made of polysilicon, and the ma...

no. 2 example

[0051] In the first embodiment, the second liner oxide layer 303 is regenerated on the sidewall and bottom surface of the annealed trench 320 to weaken the internal stress of the oxide layer, and the stress acts on the corners of the top of the trench 320 , may cause adverse effects. In order to further simplify the process, this embodiment also provides an optional method. After the step of removing the mask structure 301, a sacrificial oxide layer is formed on the surface of the exposed semiconductor substrate to improve the uniformity of silicon oxide on the corner surface. In order to weaken the adverse effect of the internal stress of the liner oxide layer 302 on the corners. The difference between this embodiment and the first embodiment lies in the step of forming the sacrificial oxide layer. Thus, in Figure 12 The process before the annealing step shown is completely the same as that of the first embodiment, and will not be repeated here.

[0052] Such as Figure ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More