Low-overhead transient fault automatic correction circuit for high speed adder

An automatic correction and adder technology, applied in instruments, electrical digital data processing, data representation error detection/correction, etc., can solve large-area overhead or delay overhead, dual-mode redundancy can only detect errors but not correct them, etc. Problems, to achieve the effect of improving resource utilization efficiency, low cost, and reducing area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The structure and working process of the low-overhead high-speed adder transient fault automatic correction circuit disclosed by the present invention will be described in detail below in conjunction with the accompanying drawings.

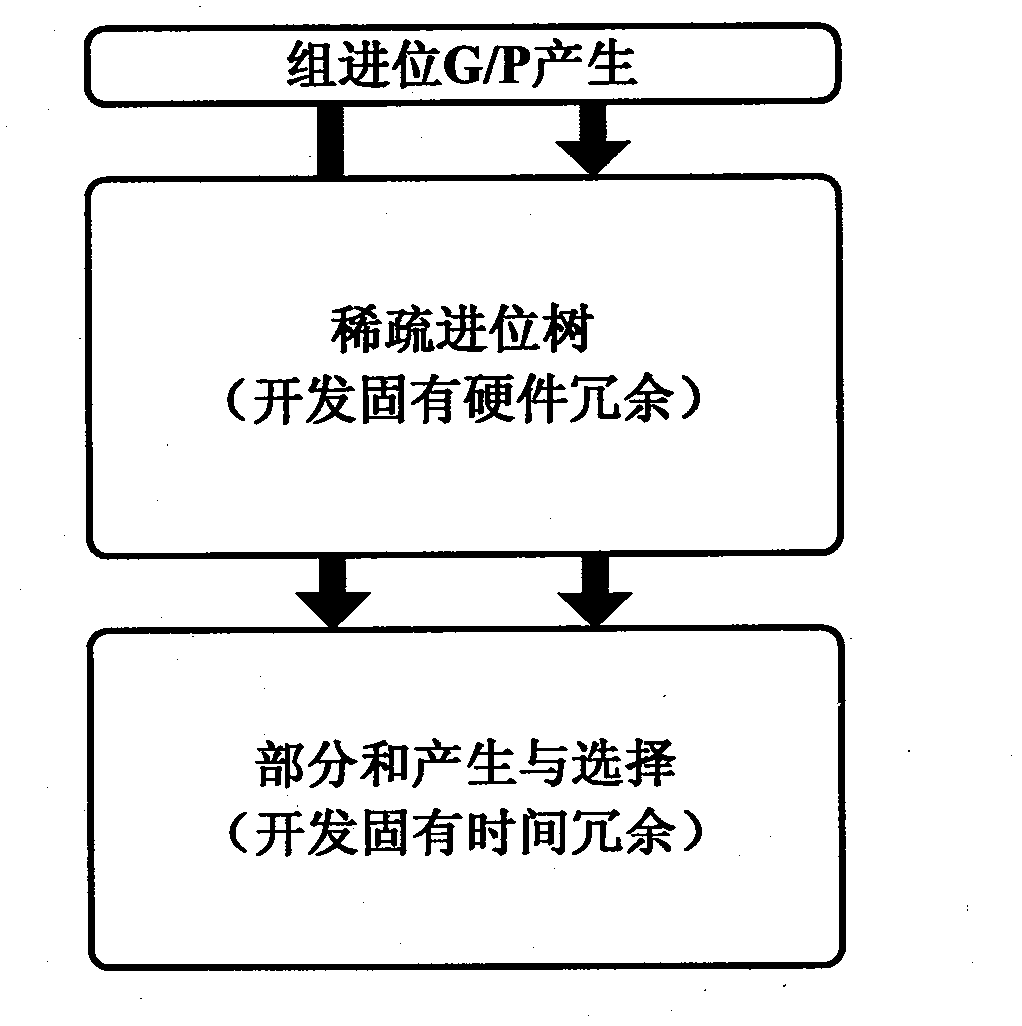

[0025] The low-overhead high-speed adder transient fault automatic correction circuit disclosed by the present invention consists of three parts, such as image 3 As shown, they are the group carry G / P generation part, the carry tree part and the partial sum generation and selection part respectively. In order to illustrate clearly, a 64-bit adder is taken as an example below. In fact, the structure of the present invention is applicable to adders of any bit width.

[0026] The group carry G / P generating part generates a 4-bit group G / P group carry signal. The input is a 4-bit A i+3 ~A i and B i+3 ~B i , after three stages of logic, the output group carry generates signal G i+3,i and group carry propagation signal P i+3,i ,Such as ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More