N type organic thin-film transistor and manufacturing method thereof

An organic thin film and transistor technology, applied in the field of N-type organic thin film transistors and their preparation, can solve the problems of limiting the development of transistors, short lifespan, and deteriorating device performance, and achieves improving carrier mobility, improving transmission capacity, and improving The effect of stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

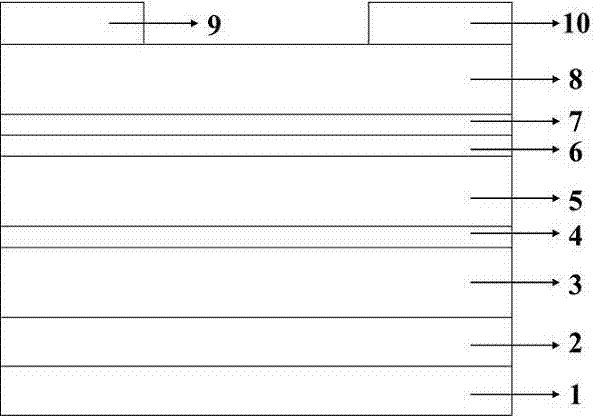

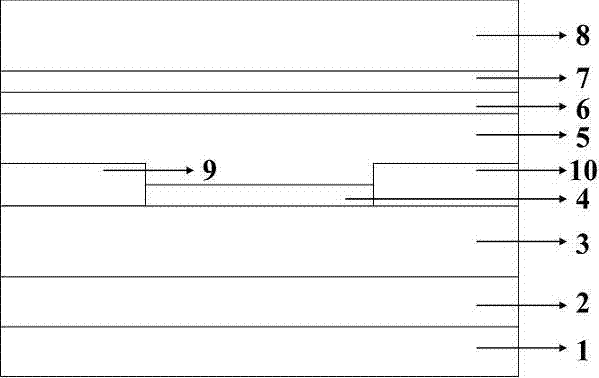

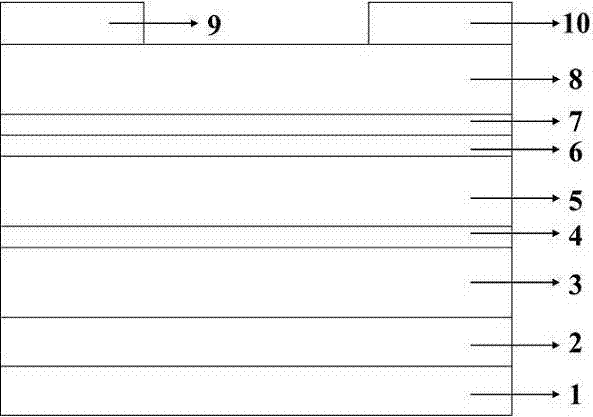

[0055] Device structure such as figure 1 shown. The material and thickness of each layer of the device are: substrate 1 is glass, gate electrode 2 is ITO, gate insulating layer 3 is PMMA (500 nm), two layers of modification layer are pentacene (2 nm), two layers of organic semiconductor The layers are all C60 (25 nm), the carrier blocking layer 6 is TAPC (2 nm), and the source electrode 9 and drain electrode 10 are both Ag (50 nm).

[0056] The preparation method of the organic thin film transistor is as follows:

[0057] ① Thoroughly clean the sputtered ITO glass substrate first, and dry it with dry nitrogen after cleaning;

[0058] ②Using the spin coating method to prepare PMMA film on ITO to form gate insulating layer;

[0059] ③Heating and baking the spin-coated PMMA film;

[0060] ④ Prepare the pentacene modified layer by vacuum evaporation;

[0061] ⑤ Prepare the first layer of C60 organic semiconductor layer by vacuum evaporation;

[0062] ⑥The TAPC carrier blocki...

Embodiment 2

[0068] Device structure such as figure 1 shown. The material and thickness of each layer of the device are: substrate 1 is glass, gate electrode 2 is ITO, gate insulating layer 3 is PVP (2000 nm), two layers of modification layer are pentacene (5 nm), two layers of organic semiconductor The layers are all C60 (80 nm), the carrier blocking layer 6 is TAPC (10 nm), and the source electrode 9 and drain electrode 10 are both Ag (150 nm).

[0069] The fabrication process of the transistor is similar to that of Example 1.

Embodiment 3

[0071] Device structure such as figure 1 shown. The material and thickness of each layer of the device are: substrate 1 is glass, gate electrode 2 is ITO, gate insulating layer 3 is PVP (1000 nm), two layers of modification layer are pentacene (3 nm), two layers of organic semiconductor The layers are all C60 (100 nm), the carrier blocking layer 6 is TCTA (20 nm), and the source electrode 9 and drain electrode 10 are both Mg (300 nm).

[0072] The fabrication process of the transistor is similar to that of Example 1.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More