CMOS (Complementary Metal-Oxide-Semiconductor Transistor) for inhibiting drain induced barrier lowering effect and manufacturing method of CMOS

A technology of sensing barriers and MOS transistors, applied in the field of CMOS devices, to achieve the effects of improved performance, low implementation cost, and simple process flow

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

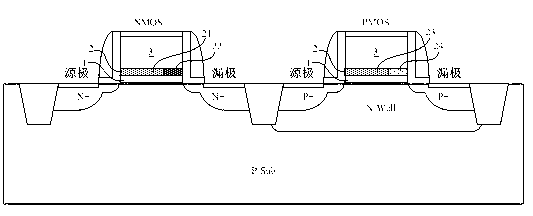

[0061] like figure 1 As shown, the gates of the N-type MOS transistor and the P-type MOS transistor of the CMOS device of the present invention all include a high dielectric layer 1, a metal oxide dielectric material layer 2 and a layer of polysilicon or metal layer 3 , and the metal oxide dielectric material layer 2 near the drain contains ions that change the work function of the metal oxide dielectric material layer 2 implanted near the drain end, and the work function of the metal oxide dielectric material The function is changed, so that the work function of the metal oxide dielectric material layer 2 near the source end and the drain end are different.

[0062] Wherein, in the metal oxide dielectric material layer 2 of the N-type MOS transistor gate, the ions are ions with a large work function, which effectively increases the metal oxide dielectric material layer 2, The work function near the drain end portion 22 makes the work function of the metal oxide dielectric ma...

Embodiment 2

[0074] And the following embodiments 2 and 3 are the same)

[0075]Step 4. Deposit a layer of polysilicon or metal layer 3 on the metal oxide dielectric material layer 2, for polysilicon or metal layer 3, thin oxide layer of N or PMOS, high dielectric layer 1 and metal oxide dielectric material Layer 2 is etched, and only part of the polysilicon or metal layer 3, the thin oxide layer of N or PMOS, the high dielectric layer 1 and the metal oxide dielectric material layer 2 for preparing the respective gates of NMOS and PMOS are reserved, Respectively form gates of NMOS and PMOS;

[0076] Step 5. Perform ion implantation in the drain-source regions of NMOS and PMOS, wherein, the drain electrode of NMOS near the first ion implantation region in the ion implantation region of NMOS; the drain electrode of NMOS near the second ion implantation region in the ion implantation region of PMOS is Drain of the PMOS.

[0077] Example 2:

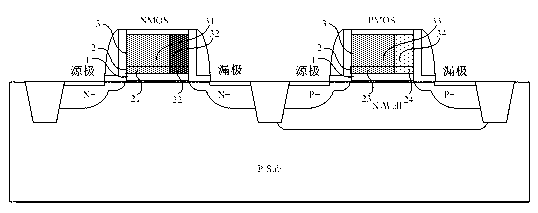

[0078] like figure 2 As shown, in this embodim...

Embodiment 3

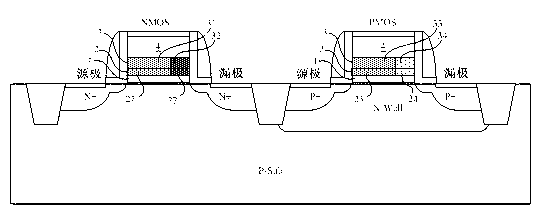

[0092] like image 3 As shown, in this embodiment, the metal oxide dielectric material layer 2 is covered with two polysilicon or metal layers, the first polysilicon or metal layer 3 and the second polysilicon or metal layer 4, wherein the The second polysilicon or metal layer 4 covers the first polysilicon or metal layer 3, and only the first polysilicon or metal layer 3 is implanted with ions of different work functions near the drain terminal. . Moreover, in this embodiment, for the entire polysilicon or metal layer (polysilicon or metal layer 3 and polysilicon or metal layer 4 ), work function adjustment is performed on half polysilicon or metal layer (Half Poly or Metal).

[0093] The difference between this embodiment and Embodiment 2 is that this embodiment includes two polysilicon or metal layers, a first polysilicon or metal layer 3 and a second polysilicon or metal layer 4 . The first polysilicon or metal layer 3 is implanted with ions that change the work function...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More