All-digital clock data recovery device and transceiver implemented thereof

A clock data recovery and clock technology, applied in the direction of digital transmission system, synchronous receiver, automatic power control, etc., can solve the problem that it is difficult to form a charge excitation circuit

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

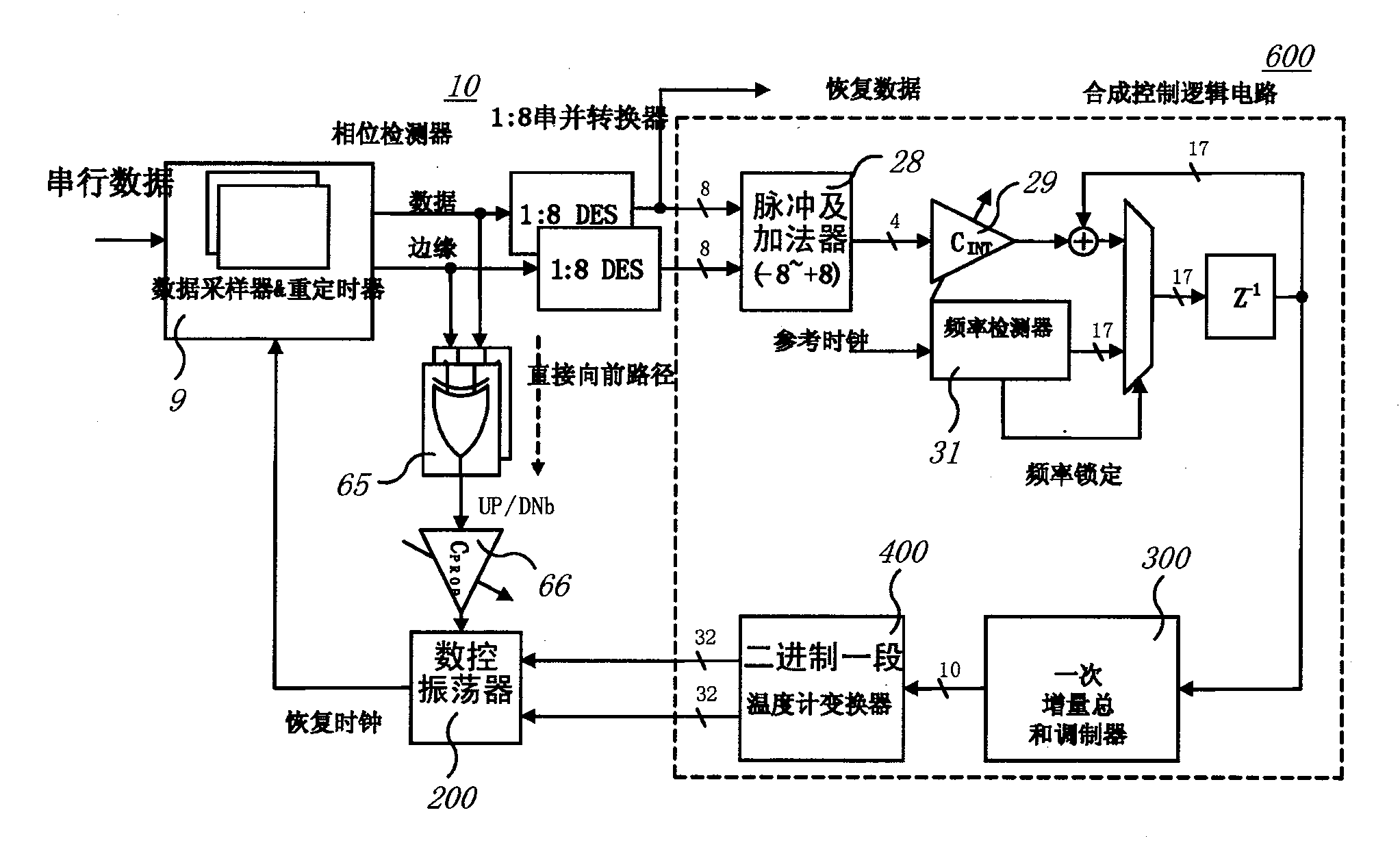

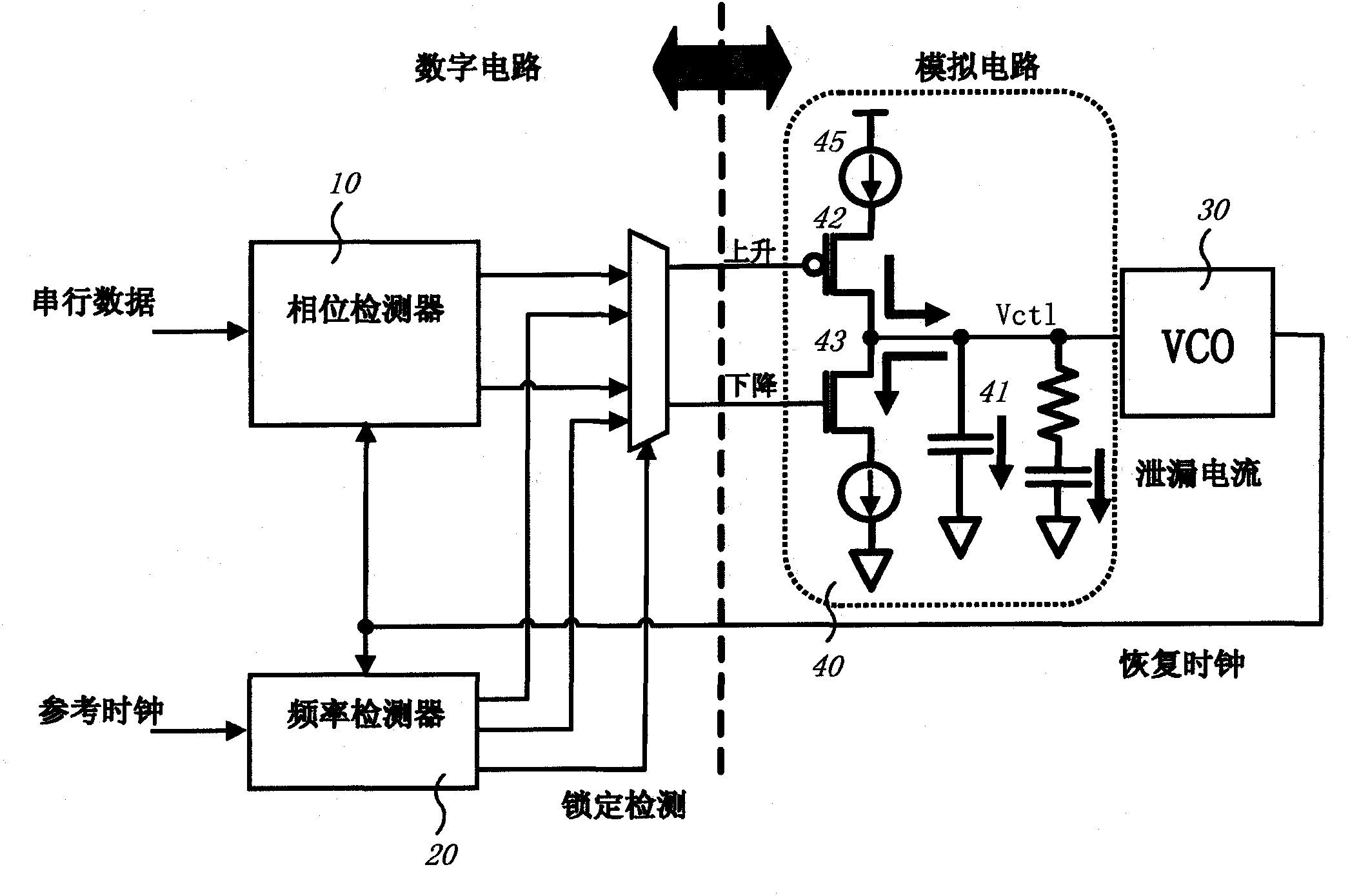

Method used

Image

Examples

Embodiment Construction

[0032] As a representative embodiment of the present invention, the PMOS transistor array (array) is composed of a variable resistance switching matrix, and the current of the PMOS transistor will be controlled according to the input signal of the logic gate, and will function as a variable resistance. At this time, the present invention proposes a method of inserting vertical resistors between rows of the switching matrix in order to equalize the low-bit frequency tuning step and the high-bit frequency tuning step. Obviously the vertical resistors consist of PMOS transistors and the logic gates are grounded.

[0033] In addition, in order to eliminate the jitter caused by the quantization error when the digitally controlled oscillator (DCO) is compared with the analog mode voltage controlled oscillator (VCO), in the present invention, the jitter ( Dithering) algorithm, for example, in order to ensure 17-bit resolution, 10-bit MSB and 7-bit LSB are dithered to prevent errors e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More