Dual-processor communication method based on SPI (serial peripheral interface) bus

A technology of SPI bus and communication method, which is applied in the direction of electrical digital data processing, instruments, computers, etc., can solve the problem of no establishment, maintenance, release management, lack of response mechanism and confirmation of whether data is received, and data frame structure does not make any Regulations and other issues, to achieve the effect of convenient application, simple expansion, and high communication rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

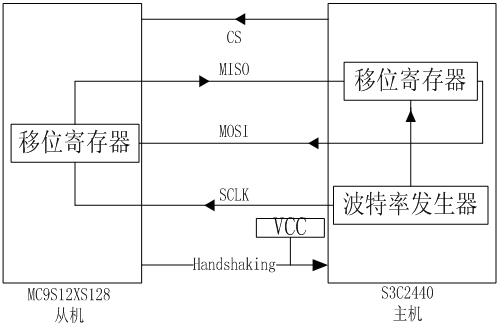

[0070] Embodiment one: see figure 1 , this dual-processor communication method based on SPI bus is characterized in that the specific operation steps are:

[0071] a. Extended SPI physical layer. On the basis of the four-wire system of SPI, add a handshake signal line connected with a pull-up resistor - HandShaking;

[0072] b. Establish a frame format based on SPI bus two-way communication;

[0073] c. Based on the CS signal line already stipulated by the SPI bus and our newly established HandShaking handshake signal line, a synchronization mechanism based on the two-way communication of the SPI bus is established;

[0074] d. On the basis of sending frame and receiving frame format, establish a flow control mechanism;

[0075] e. Based on the CRC checksum and frame checksum confirmation, an error handling mechanism is established.

Embodiment 2

[0077] see Figure 1 to Figure 6 , the present embodiment is basically the same as Embodiment 1, and the special features are as follows:

[0078] The method of the extended SPI physical layer of described step a is:

[0079] On the basis of SPI four-wire communication, establish a five-wire system for two-way communication SPI bus, that is, add a handshake signal line connected with a pull-up resistor on the basis of SPI four-wire system-HandShaking, which is a slave to The host is a one-way signal line. The function of the HandShaking signal is to inform the host that the slave has data to send.

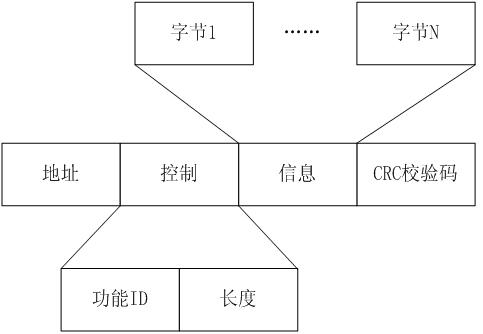

[0080] Described step b sets up the method based on SPI bus two-way communication frame format as:

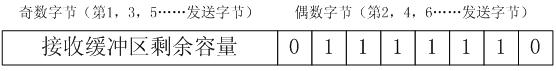

[0081] On the basis of the five-wire SPI bus, adopt the "0-bit insertion method", and use (0x7f) as a sign of flow control; as the master-slave communication mode, the frame format mainly includes the sender's frame format and the receiver's frame format Two kinds:

[0082] ①, s...

Embodiment 3

[0105] Figure 7 Shown is a system architecture diagram of a body network control device. There are two processors ARM9 and S12 in the system, of which ARM9 is the host and S12 is the slave.

[0106] The communication method described in this patent is used as the communication interface between the ARM9 module and the S12 processor. The S12 processor is responsible for the communication of KWP2000 bus, CAN bus and LIN bus, and the ARM9 module is responsible for the display and touch operation of the touch screen. The function IDs used in this application include:

[0107] Table 1 Body bus network controller communication ID

[0108] Function ID number Functional description 0x00 Slave processor control operation sent by ARM 0x01 CAN bus data information sent by ARM 0x02 LIN bus data information sent by ARM 0x03 KWP2000 bus data information sent by ARM 0x10 Slave status information sent by S12 0x11 CAN bus data information sent...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More