Opening filling method

A filling method and mask layer technology, applied in semiconductor/solid-state device components, vacuum evaporation plating, coating, etc., to achieve the effects of improving reliability, avoiding necking, and eliminating the probability of void defects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0036] Figure 5 It is a flow chart of the filling method of the opening in the present embodiment, Figure 6 to Figure 11 It is a schematic diagram of the opening filling method in this embodiment. In this embodiment, the process of filling via holes between metal wiring layers is taken as an example, and the openings are via holes.

[0037] As shown, the method of filling the opening includes:

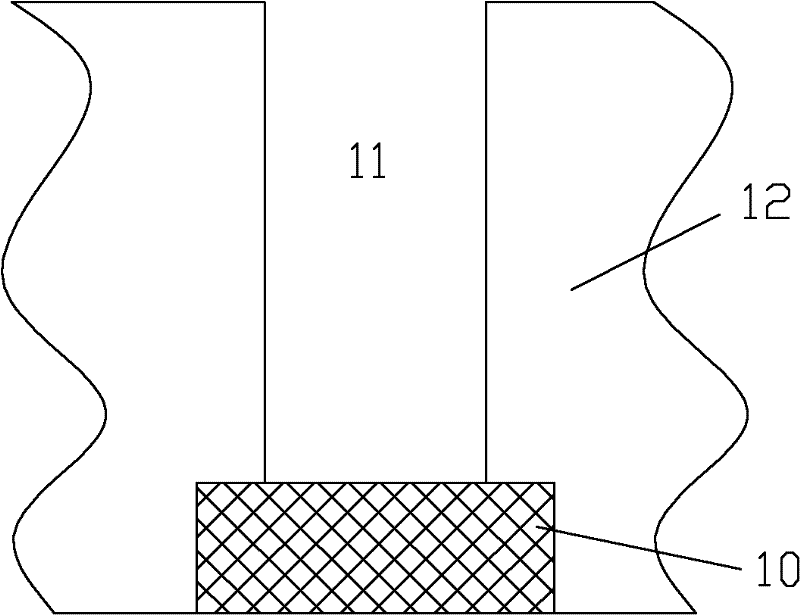

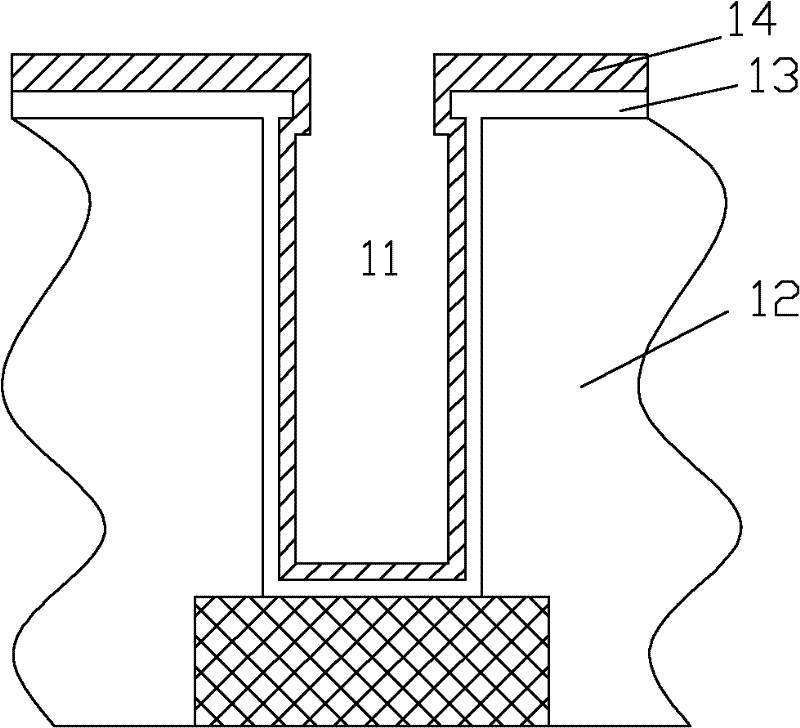

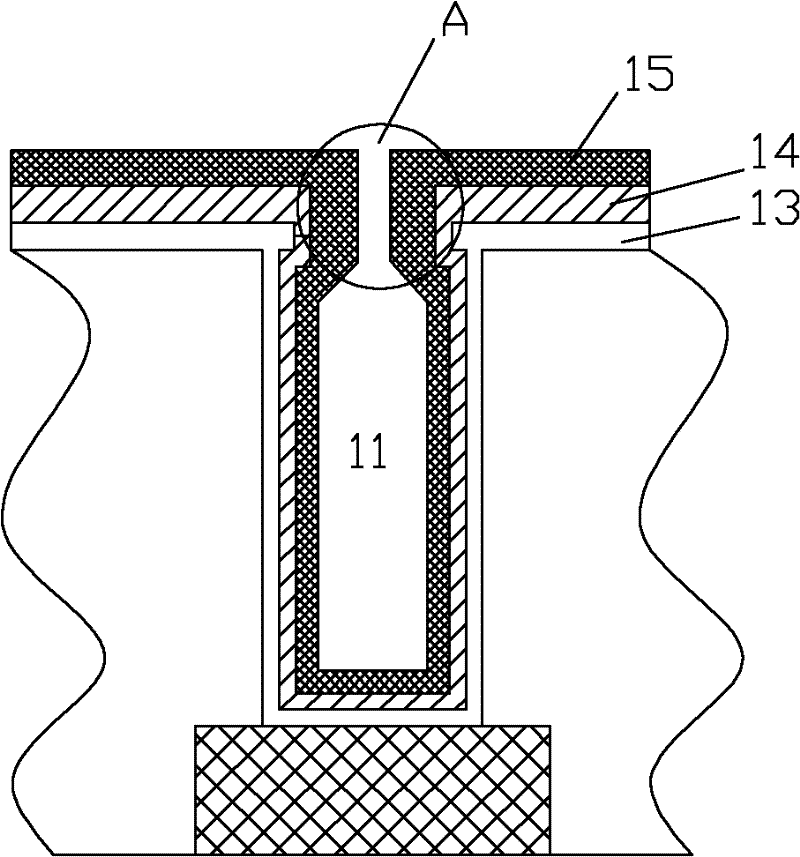

[0038] Step S1: Provide a semiconductor substrate, refer to Figure 6 As shown, the semiconductor substrate has at least an underlying metal wiring layer 101 and an isolation dielectric layer 102 above the underlying metal wiring layer 101 , and the isolation dielectric layer 102 has a through hole 103 therein. Here, the "bottom layer" is only relative to the metal wiring layer above it, and does not represent the first metal wiring layer. The semiconductor substrate also includes logic devices, power devices and / or storage devices (not shown in the figure), etc., which are locat...

Embodiment 2

[0060] Figure 13 It is a schematic diagram of the opening filling method in this embodiment. The filling method of described opening comprises:

[0061] A semiconductor substrate is provided, having at least an underlying metal wiring layer and an isolation dielectric layer above the underlying metal wiring layer, and an opening is provided in the isolation dielectric layer;

[0062] sequentially forming a diffusion barrier layer and a seed layer on the surface of the isolation medium layer inside and outside the opening;

[0063] forming a mask layer on the surface of the seed layer outside the opening;

[0064] Covering a metal layer on the semiconductor substrate with a mask layer, the metal layer filling the opening;

[0065] The planarization process is performed to remove the metal layer, the seed layer and the diffusion barrier layer outside the opening, so as to form a metal wiring layer.

[0066] The difference from the embodiment in the above steps is, as Figu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More