NAND flash memory controller supporting operation out-of-order execution

A memory controller and flash memory control technology, which is applied in the direction of instruments, electrical digital data processing, etc., can solve the problem of limited number of memory access operations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

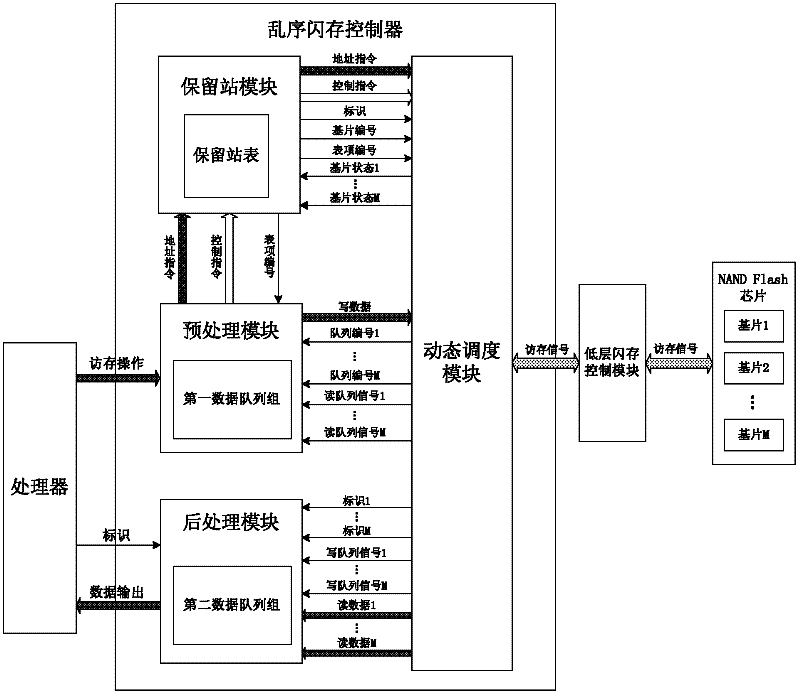

[0050] figure 1 Is the overall structure block diagram of the present invention.

[0051] The present invention is placed between the processor CPU and the low-level flash memory control module, the low-level flash memory control module is connected with the chip, the chip is a NAND Flash chip, and contains M substrates inside, and M is a positive integer power of 2, generally 4. The invention is composed of a preprocessing module, a reservation station module, a dynamic scheduling module and a postprocessing module. The low-level flash memory control module connected with the present invention is formed by parallel connection of M sequential memory controllers mentioned in the background art, and respectively controls M substrates in the chip.

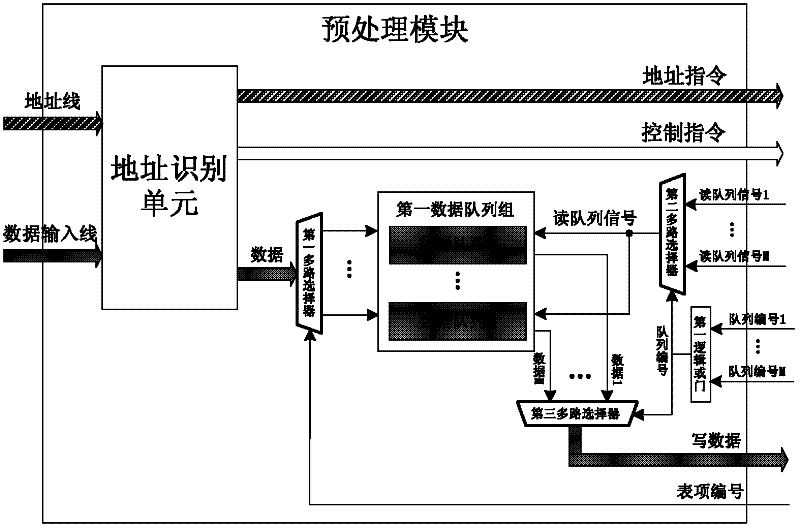

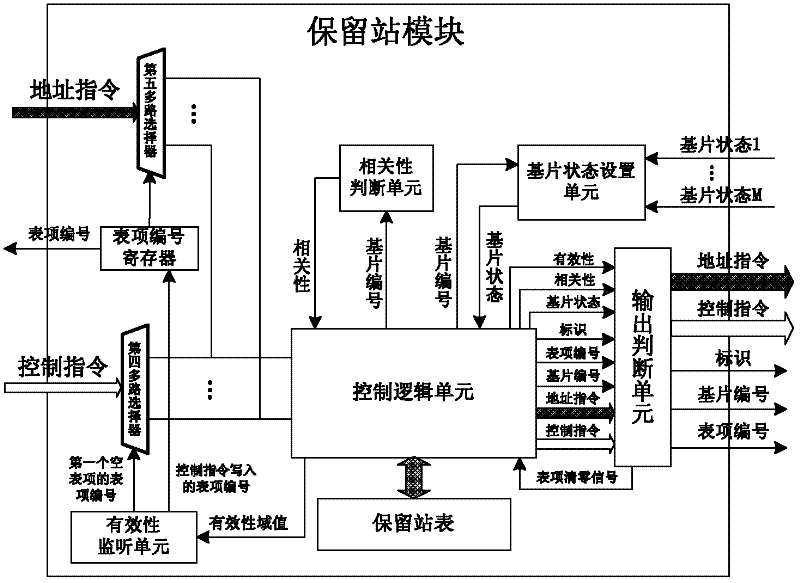

[0052] The preprocessing module is connected with the processor, the reservation station module, and the dynamic scheduling module, and contains the first data queue group. The preprocessing module receives control instructions and a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More