Amplitude detection circuit with direct current offset elimination function

A DC offset and amplitude detection technology, applied in electrical components, transmission monitoring, transmission systems, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

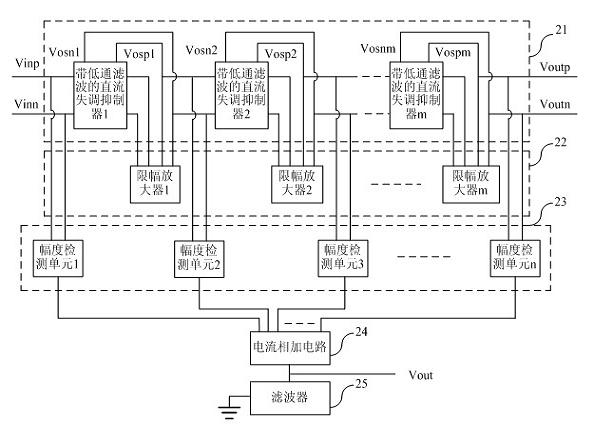

[0064] Figure 2a The block diagram of the amplitude detection circuit with the function of eliminating the DC offset according to the embodiment of the present invention is given. The amplitude detection circuit with DC offset cancellation function is composed of a DC offset suppression circuit 21 including an M-level DC offset suppressor with low-pass filtering, an amplitude limiting amplifier circuit 22 including an M-level limiting amplifier, and an N-level amplitude detection unit. The detection circuit 23 , the current addition circuit 24 and the filter 25 are constituted. The differential detection signal is connected to the differential input terminal of the amplitude detection circuit with the DC offset cancellation function, and is connected to the differential input terminal of the first-stage amplitude detection unit and the differential input terminal of the first-stage DC offset suppressor with low-pass filtering. The differential input terminal of the amplifier...

no. 2 example

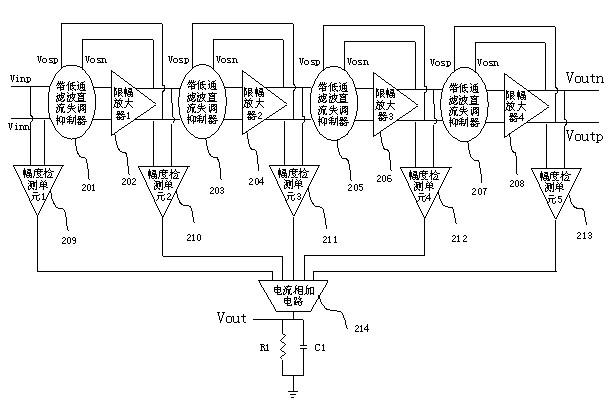

[0066] Figure 2b The block diagram of the amplitude detection circuit with the function of eliminating the DC offset according to the embodiment of the present invention is given. Set M to 4, and N=M+1. The amplitude detection circuit with the DC offset cancellation function of the embodiment includes the first-stage-fourth-stage DC offset suppressors 201, 203, 205 and 207 with low-pass filtering, the first-stage-fourth-stage limiting amplifier 202, 203 , 206 and 208 , the first to fifth stage amplitude detection units 209 , 210 , 211 , 212 and 213 , and the sum 208 , the current summing circuit 214 and the low-pass filtering circuit 215 . combine Figure 2b Describe the realization of the amplitude detection function in the present invention:

[0067] The differential input signals Vinn and Vinp are input to the first-stage DC offset suppressor 201 with low-pass filtering, and at the same time, they are subtracted from the low-pass filtered signal of the output of the cur...

no. 3 Embodiment

[0073] Image 6 The circuit diagram of another embodiment of the DC offset suppressor with low-pass filtering is given. Except for omitting the load tubes M8 and M9 connected by diodes, the circuit is basically the same as Image 6same.

[0074] The circuit includes two parts, a low-pass filter and a DC offset subtractor. The low-pass filter extracts the DC component in the data amplified by the next stage limiting amplifier. The low-pass filter is composed of an active resistor and a passive capacitor. The active resistor is realized by a multi-stage cascaded MOS tube working in the linear region. The resistance value of the resistor can be made very large, and the area occupied is relatively small. The value of the capacitance can be relatively small, so that both the resistance and the capacitance can be realized on the chip, which saves the cost of the chip. The subtraction of the input of the signal in the DC offset suppressor with low-pass filtering and the input of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More