Side wall cavity layer structure of semiconductor device and method for preparing side wall cavity layer structure

A technology of semiconductor and layer structure, which is applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of enlargement and reduction of side wall thickness, and achieve the effect of simple structure and weakened gate potential. The effect of the method is simple and easy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The present invention will be explained in detail below in conjunction with the accompanying drawings.

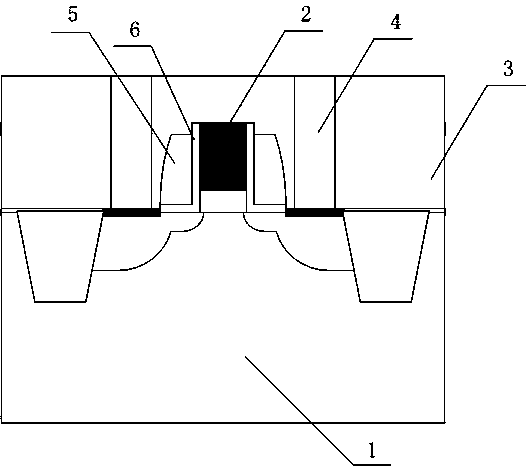

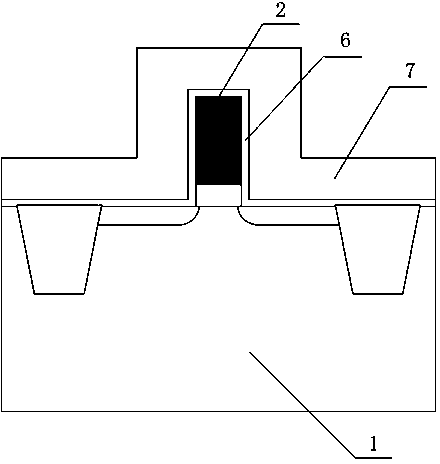

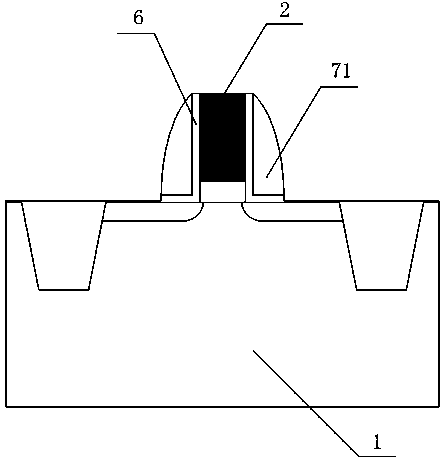

[0030] Such as figure 1 A sidewall cavity layer structure of a semiconductor device according to an embodiment of the present invention shown in , includes a semiconductor substrate 1 , a gate 2 , a dielectric layer 3 and a contact hole 4 . The outer side of the gate 2 is provided with a void layer 5, and between the void layer 5 and the gate 2 and the semiconductor substrate 1 is provided with SiO 2 Layer 6.

[0031] The present invention effectively reduces the dielectric constant of the sidewall material by introducing a void layer in the sidewall, thereby weakening the effect that the fringe electric field of the source and drain of the device affects the channel through the capacitive coupling of the sidewall and the capacitive coupling of the contact hole through the sidewall Effects on the gate potential.

[0032] In an embodiment of the present invention, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More