Clock generation circuit and analogue-to-digital converter (ADC) sampling circuit

A clock generation circuit and clock signal technology, applied in electrical components, electrical signal transmission systems, analog-to-digital converters, etc., can solve problems such as limited increase in clock signal voltage value, complex circuit structure, and variable on-resistance of transistor switches. , to achieve the effect of improving response speed, reducing harmonic distortion and small equivalent resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 2

[0074] The working process of the clock generating circuit in the second embodiment is similar to that in the first embodiment, and will not be repeated here.

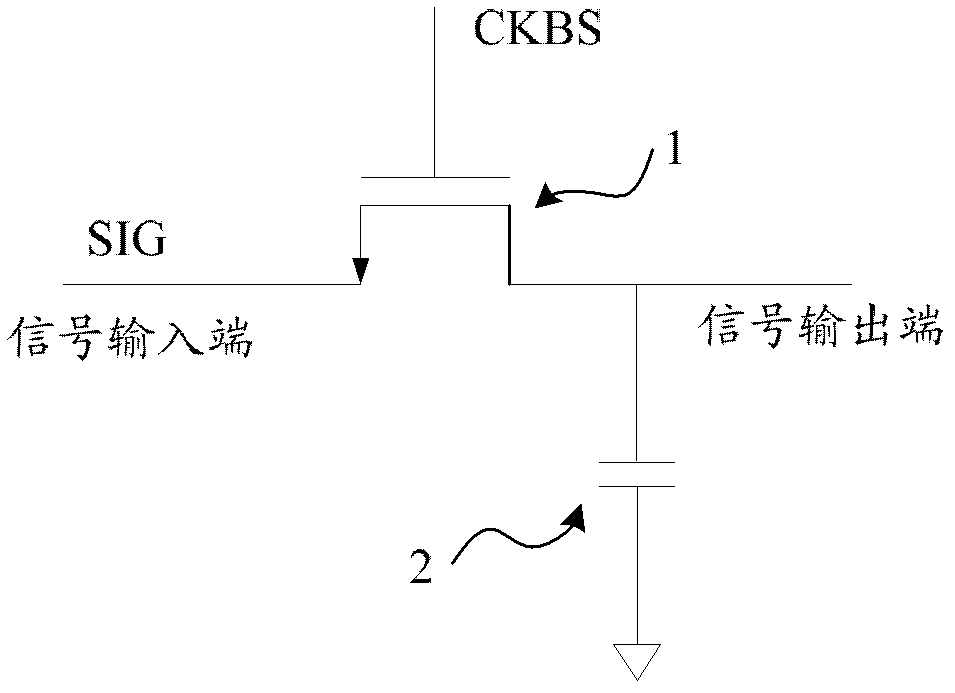

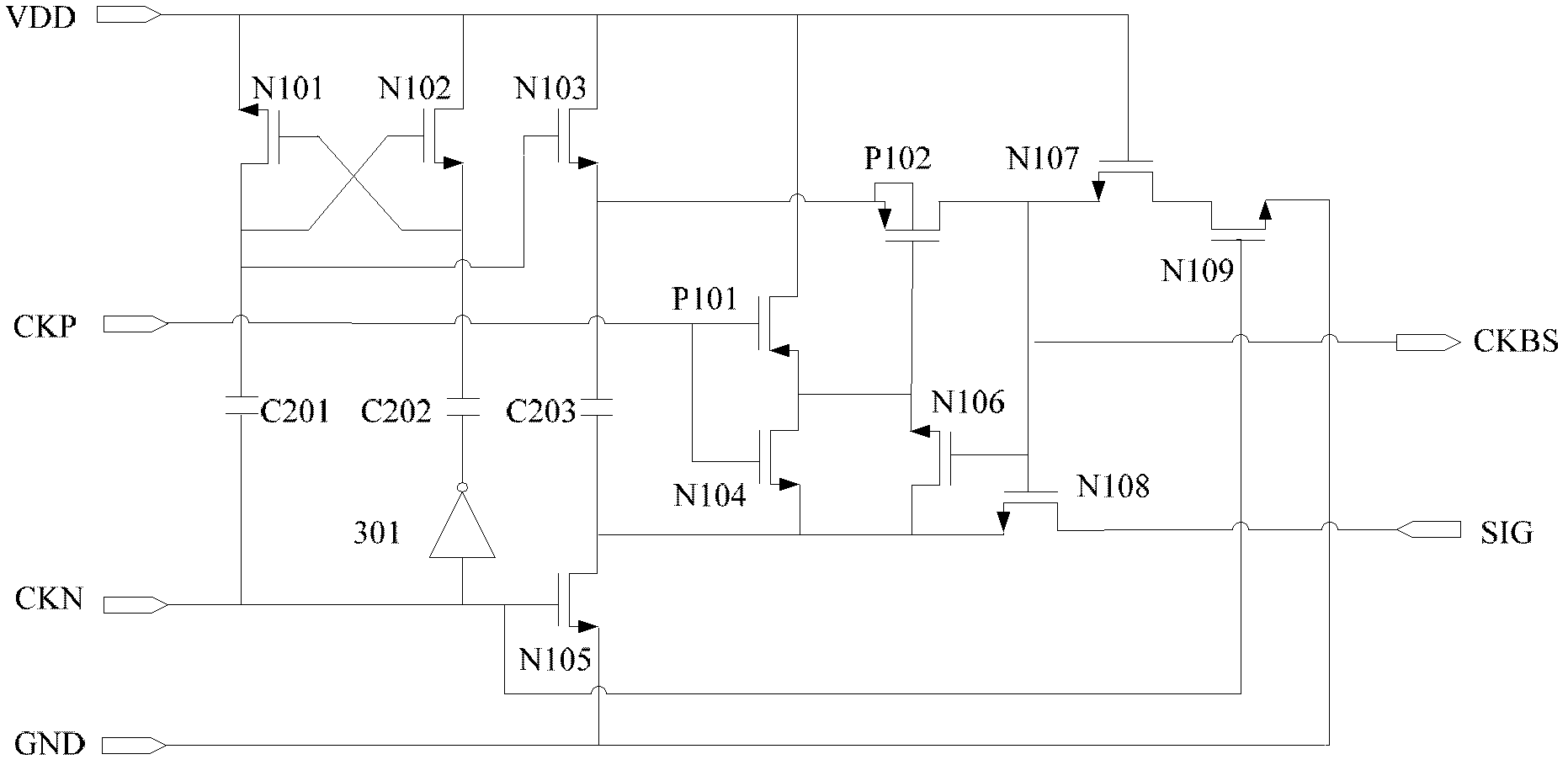

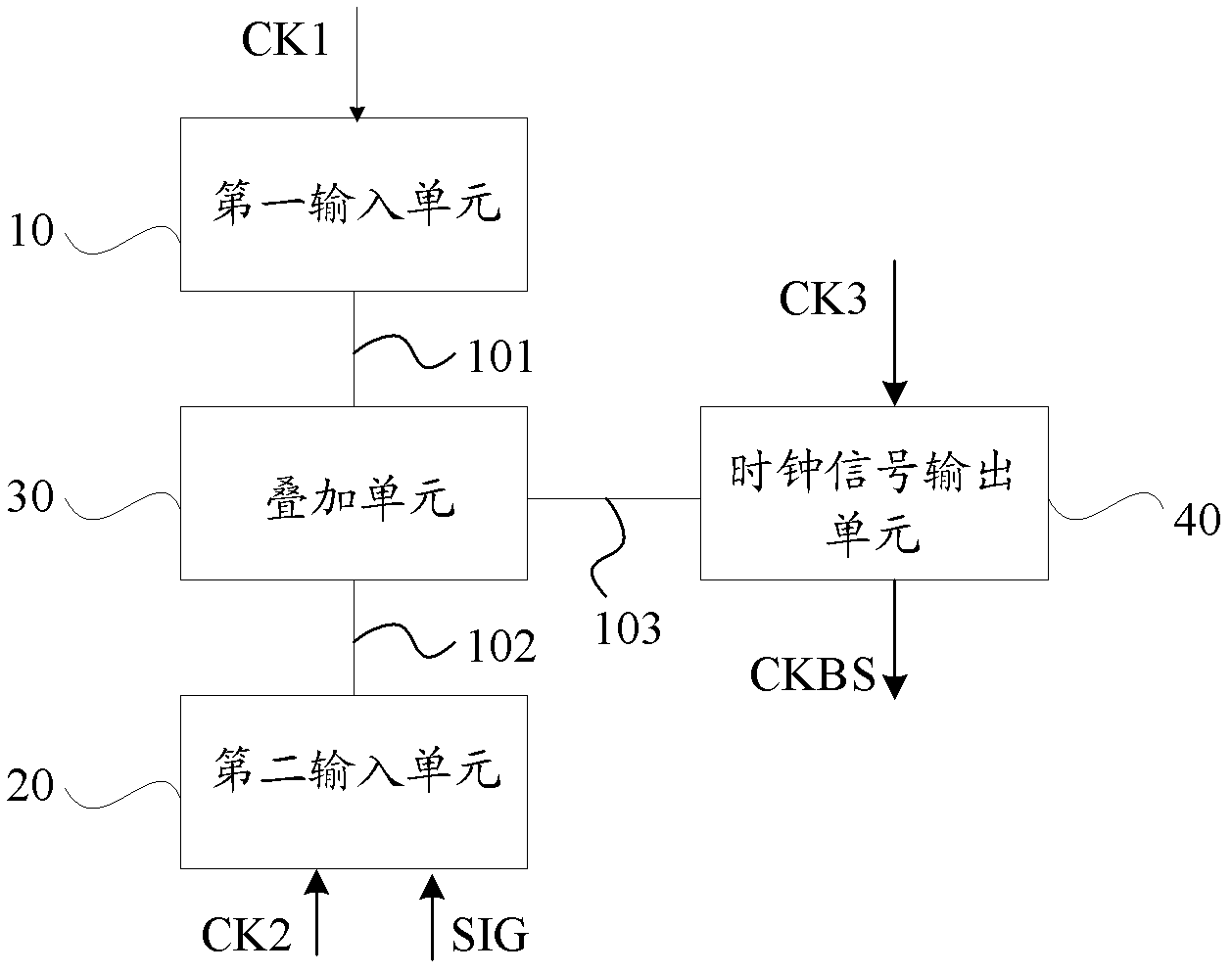

[0075] Figure 7 A schematic diagram of a waveform of a clock signal generated by superimposing a voltage pulse signal and an analog pulse signal is shown. Depend on Figure 7 It can be seen that the voltage value of the clock signal CKBS is the sum of the power voltage of the bias power VDD and the voltage of the analog signal SIG. Combined with the above formula, for an NMOS transistor, the gate input clock signal CKBS, the source input analog signal SIG, so V g -V in Certainly, that is, the equivalent resistance R of the NMOS transistor switch is constant, and the NMOS transistor switch can be regarded as a constant conductance switch.

[0076] It should be noted that, the first pulse control signal CK1, the second pulse control signal CK2 and the third pulse control signal CK3 can be based on the first input un...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More