High-speed low power consumption true single-phase clock 2D type two-thirds dual-mode frequency divider

A technology of true single-phase clock and dual-mode frequency divider, which is applied in the field of frequency synthesizer to achieve the effect of increasing operating frequency, reducing power consumption, and reducing the number

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] Below, in conjunction with the embodiments and with reference to the accompanying drawings, the specific implementation modes of the present invention will be described in detail, so that the technical solutions and beneficial effects of the present invention can be further described.

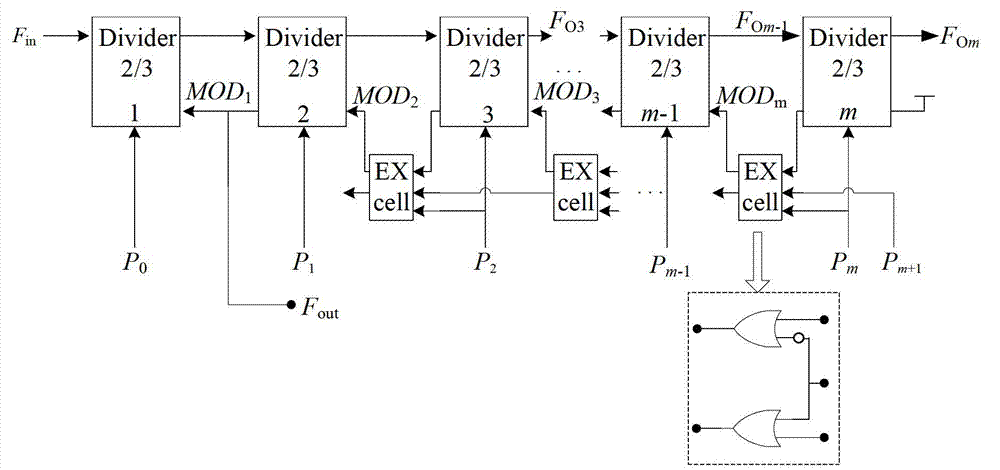

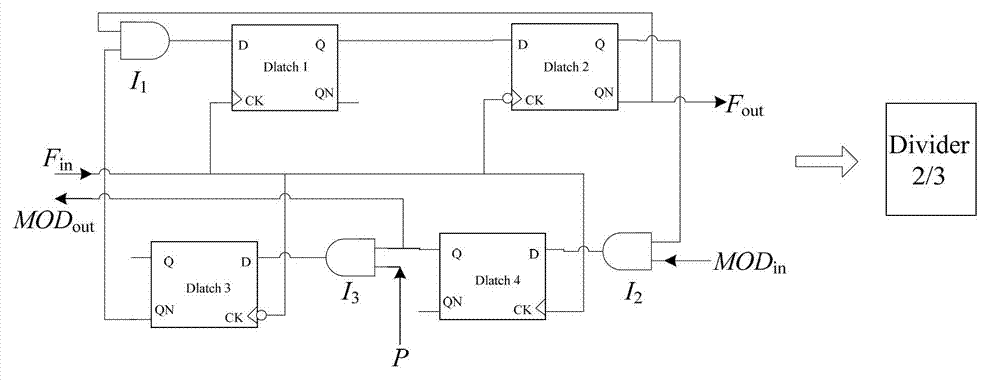

[0020] The high-speed and low-power true single-phase clock 2D type 2 / 3 dual-mode frequency divider proposed by the invention is used in the multi-mode frequency divider with cascaded 2 / 3 frequency divider structure. A schematic diagram of a 2 / 3 cascaded multi-mode frequency divider is shown in Figure 1. The multi-mode frequency divider is composed of cascaded 2 / 3 dual-mode frequency divider units. The m-level 2 / 3 dual-mode Take the frequency divider unit cascading as an example, the first stage is the highest frequency input, the corresponding output of the previous stage is used as the input of the next stage, and the output MODout of the latter stage is fed back and combined with the m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com