Super-junction vertical double-diffusion metal-oxide-semiconductor (VDMOS) device with dynamic charge balance

A charge balancing and dynamic technology, applied in electrical components, semiconductor devices, circuits, etc., can solve the problems of limiting the forward safe working area of the device, device temperature rise, device failure, etc., to expand the forward safe working area, alleviate the charge Unbalance, the effect of increasing the current range

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

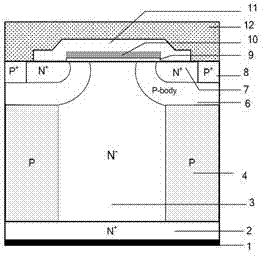

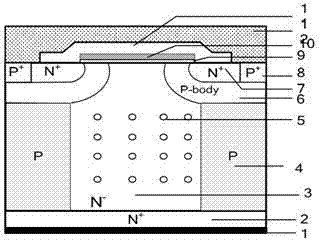

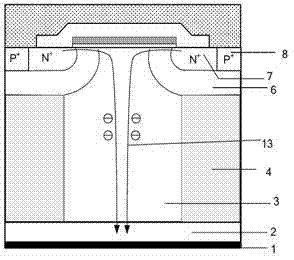

[0024] A super junction VDMOS device with dynamic charge balance, its structure is as figure 2 Shown, including N + Substrate 2, located at N + The metalized drain electrode 1 on the back of the substrate 2 is located at N + The super junction structure on the front side of the substrate 2; the super junction structure consists of N - The epitaxial region 3 and the P-type pillar region 4 are formed alternately; there is a P-type base region 6 on both sides of the top of the super junction structure, and the P-type base region 6 is connected to the N - The epitaxial region 3 is in contact with the P-type pillar region 4; each P-type base region 6 has an N + Source area 7 and a P + Body area 8, N + Source area 7 and P + The two body regions 8 are in contact with the metalized source electrode 12; the gate oxide layer 9 covers the two P-type base regions 6 and the N between them. - On the surface of the epitaxial region 3, the upper surface of the gate oxide layer 9 is a polysilicon ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More