MEMS (micro-electromechanical systems) device and vacuum encapsulation method of wafer level thereof

A device and silicon structure technology, which is applied in the field of MEMS devices and their vacuum packaging based on silicon-silicon bonding technology, can solve the problems of poor air tightness and difficult electrical interconnection of MEMS devices in wafer-level vacuum packaging, and is convenient for promotion and application. , Reduce the cost of packaging, good air tightness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

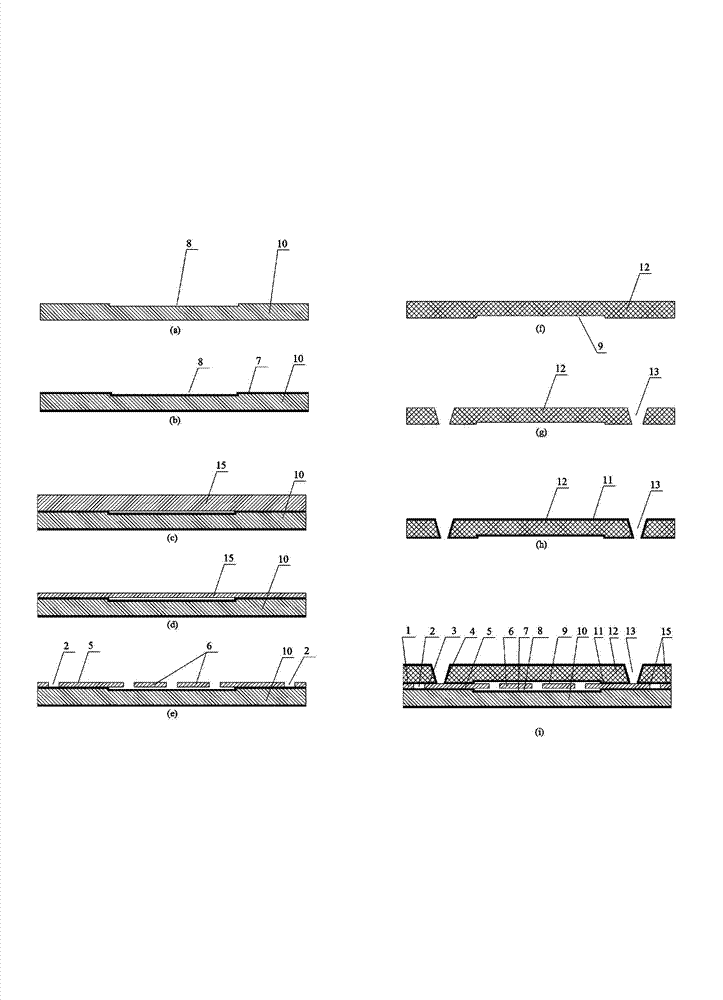

[0021] The present invention will be further described below in conjunction with the accompanying drawings.

[0022] 1. MEMS device structure:

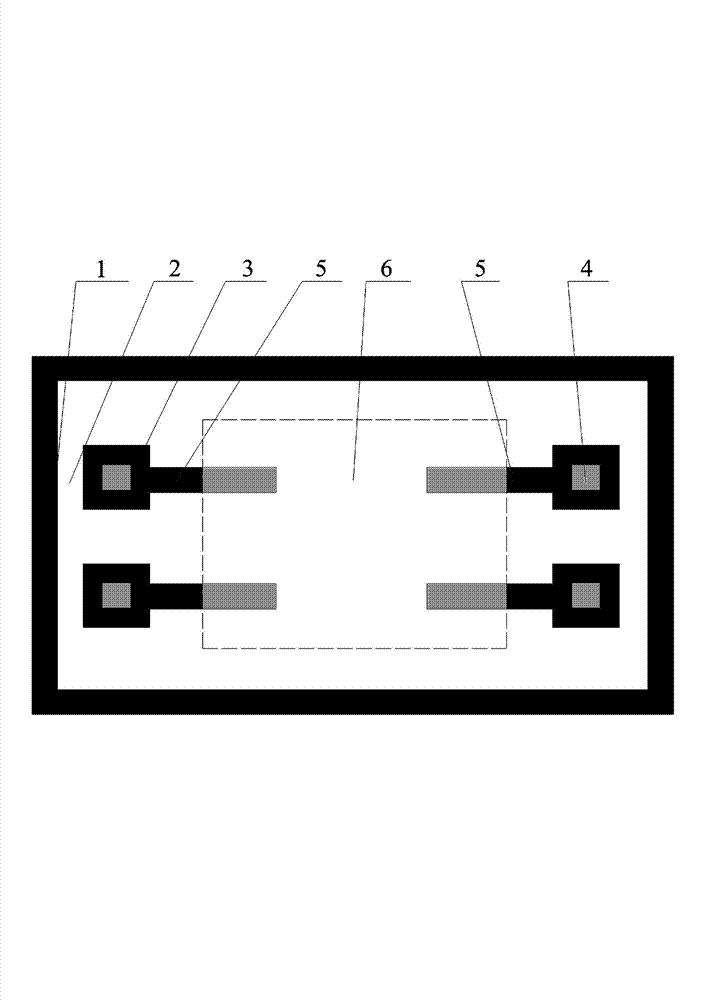

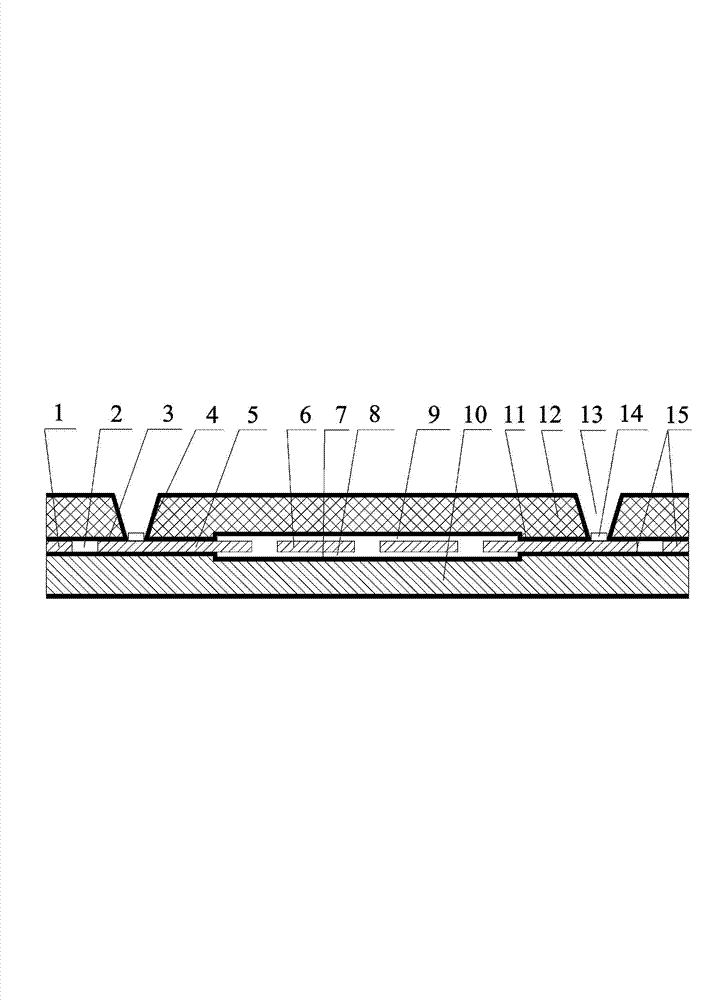

[0023] Such as figure 1 , figure 2 As shown, the MEMS device is composed of a silicon substrate layer 10 , a silicon structure layer 15 and a silicon capping layer 12 .

[0024] The surface of the silicon substrate 10 is etched to form a shallow cavity 8, so that a certain distance is formed between the movable structure 6 and the substrate, so as to avoid hindering the movement of the movable structure. The silicon capping layer 12 etches the shallow cavity 9 and the lead through hole 13 , and the position and shape of the shallow cavity 9 correspond to that of the shallow cavity 8 on the silicon substrate. The surfaces of the silicon substrate 10 and the silicon cap 12 respectively have a certain thickness of an oxide layer 7 and an oxide layer 11 , which are bonded to the silicon structure layer 15 to play an insulating role. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More