Manufacturing method of MOS (metal oxide semiconductor) transistor

A technology for MOS transistors and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as low junction capacitance and junction leakage performance, inability to meet, and achieve lower junction capacitance, junction leakage, and control. The effect of the short channel effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

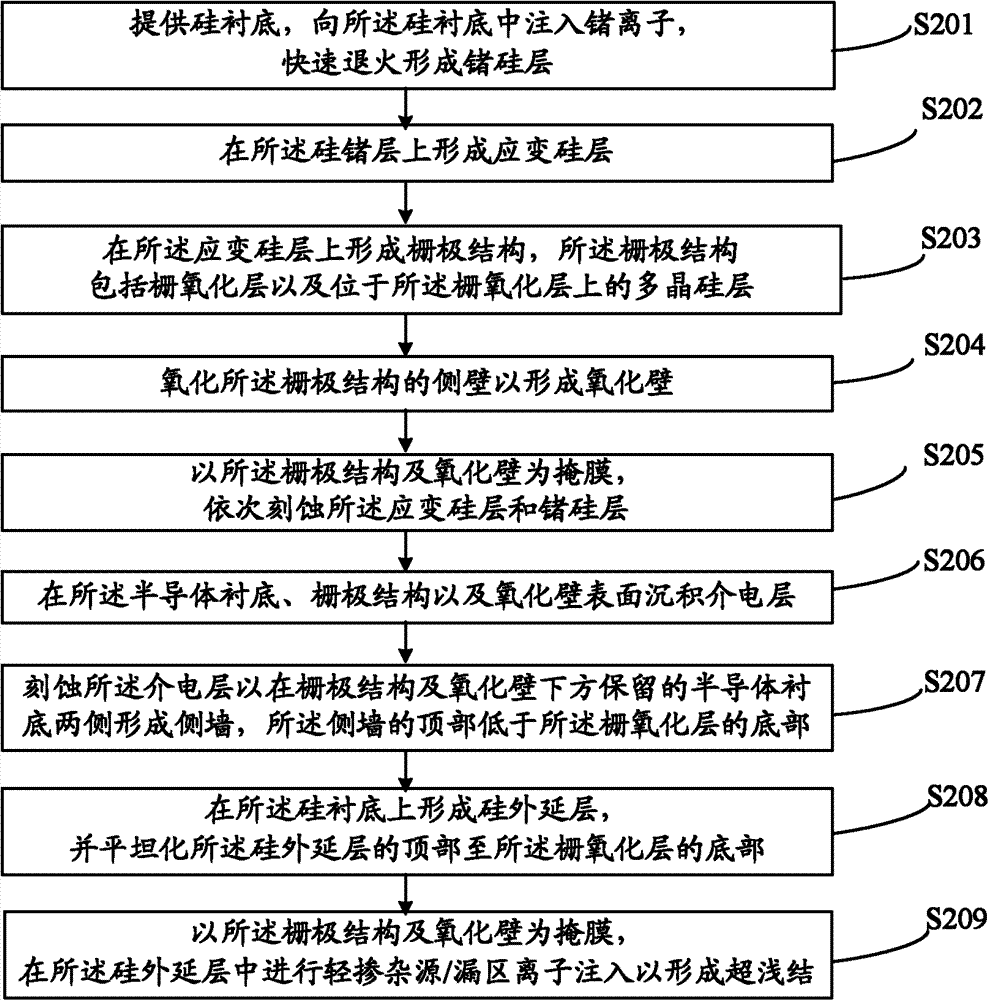

[0039] The invention provides a method for manufacturing a MOS transistor, the method comprising the steps of:

[0040] Provide semiconductor substrates;

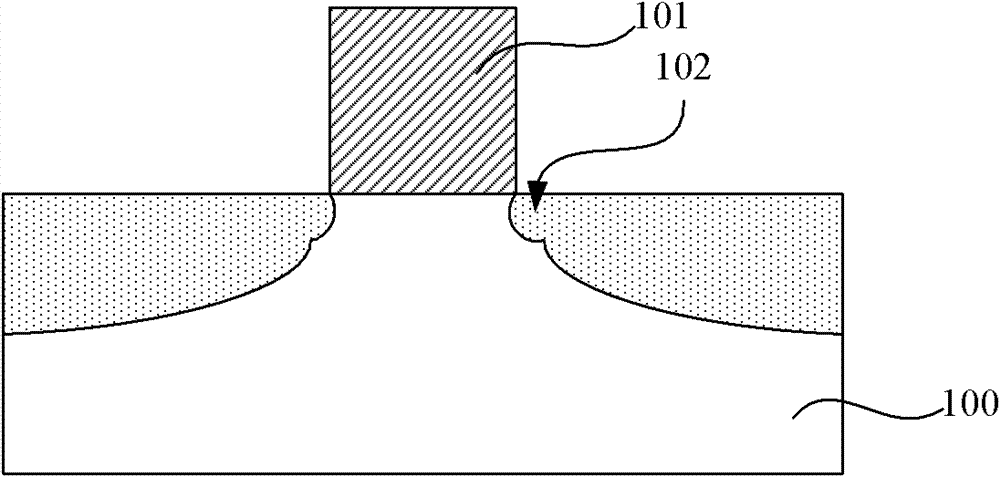

[0041] forming a gate structure on the semiconductor substrate, the gate structure comprising a gate oxide layer and a polysilicon layer on the gate oxide layer;

[0042] oxidizing sidewalls of the gate structure to form oxide walls;

[0043] using the gate structure and the oxide wall as a mask to remove part of the semiconductor substrate;

[0044] Depositing a dielectric layer on the surface of the semiconductor substrate, the gate structure and the oxide wall;

[0045] Etching the dielectric layer to form sidewalls on both sides of the semiconductor substrate remaining under the gate structure and the oxide wall, the top of the sidewall is lower than the bottom of the gate oxide layer;

[0046] forming a silicon epitaxial layer on the semiconductor substrate from the top to the bottom of the gate oxide layer;

[004...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Width | aaaaa | aaaaa |

| Height | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More