Low-cost TSV (through silicon via) three-dimensional integration process method

A process method and low-cost technology, applied in the field of microelectronics, can solve the problems of expensive investment in special equipment, difficult to remove the bottom insulating film, and difficult to protect the side wall of the hole, so as to save investment in special equipment, save special equipment, reduce cost effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

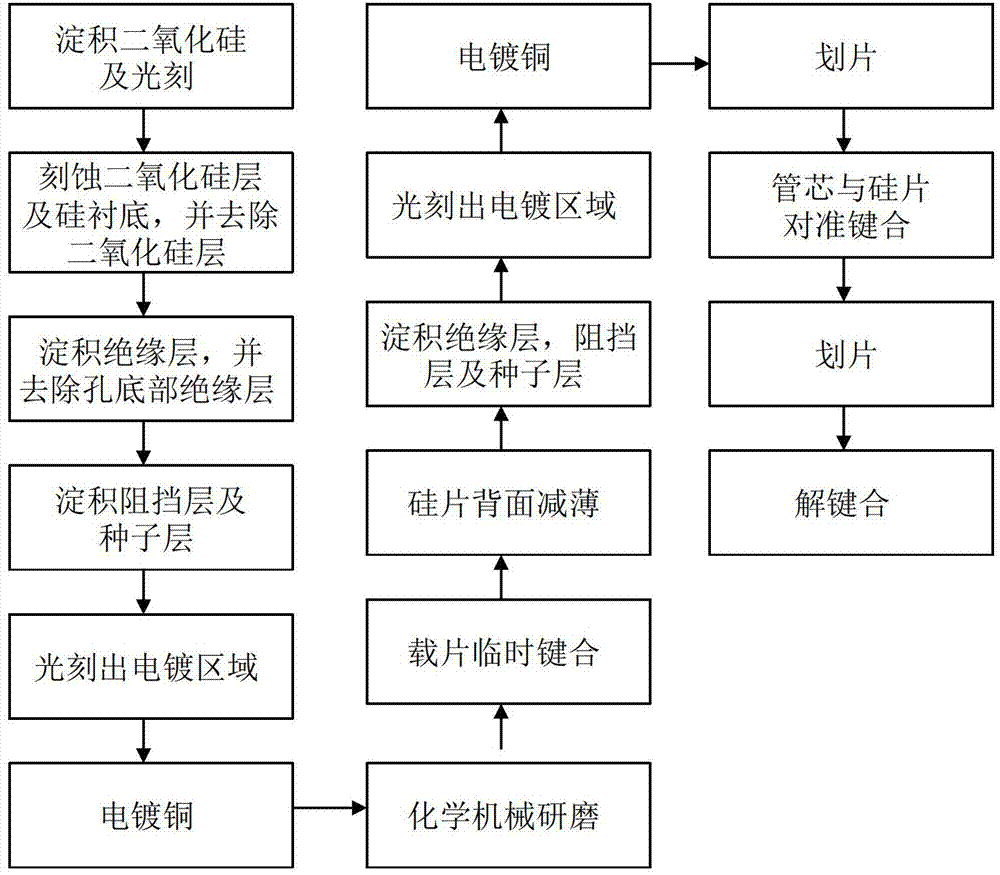

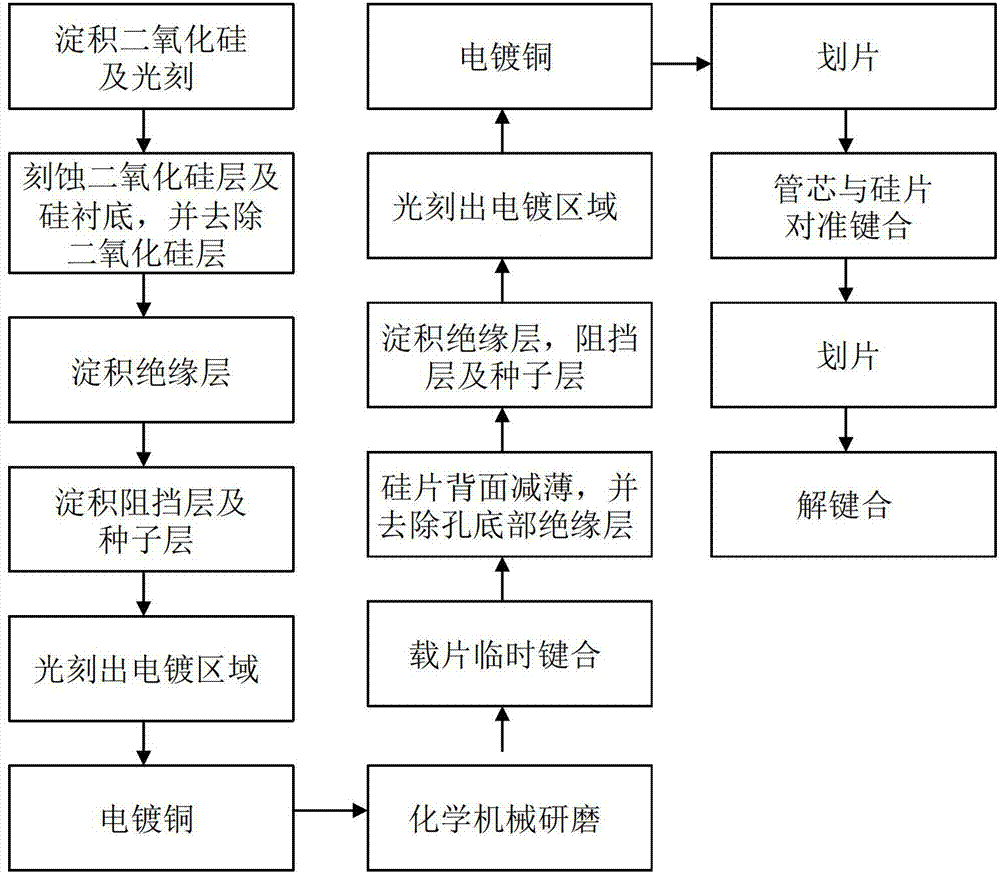

Method used

Image

Examples

Embodiment 1

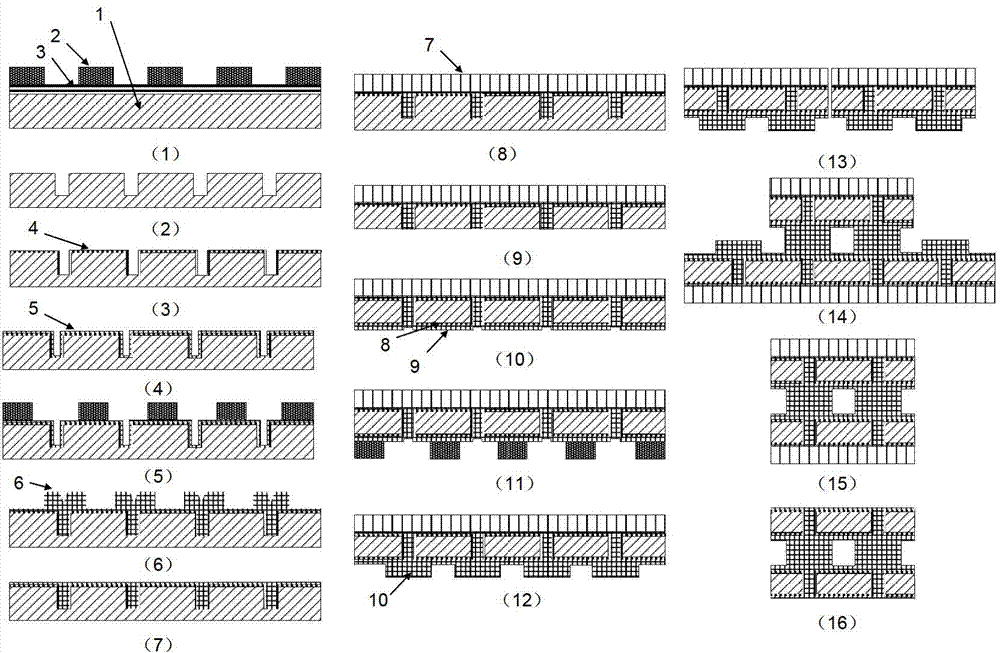

[0037] 1. Use Cz silicon (100) (0.1~0.2Ω·cm) substrate; use LPCVD to deposit silicon dioxide 1500A, coat photoresist 10000A on the surface of the silicon wafer, expose and develop, and expose the silicon dioxide with a width of 200000A silicon surface

[0038] 2. Etch silicon dioxide to the surface of the silicon substrate, and continue to etch the silicon substrate to form a TSV hole with a depth of 500000A;

[0039]3. SPM cleaning to remove the photoresist on the surface, and LPCVD to deposit a silicon dioxide insulating film 150A;

[0040] 4. Using ion sputtering to grow the barrier layer tantalum nitride 150A, and the seed layer copper 150A;

[0041] 5. Apply photoresist 10000A on the surface of the silicon wafer again, expose, develop, and expose the window that needs copper plating;

[0042] 6. Electroplate copper 600000A on the surface of the silicon wafer, and use SPM to clean and remove the photoresist;

[0043] 7. Using chemical mechanical grinding, grinding to th...

Embodiment 2

[0054] 1. Use Cz silicon (100) (0.1~0.2Ω·cm) substrate; use LPCVD to deposit silicon dioxide 1500A, coat photoresist 10000A on the surface of the silicon wafer, expose and develop, and expose the silicon dioxide with a width of 250000A silicon surface

[0055] 2. Etch silicon dioxide to the surface of the silicon substrate, and continue to etch the silicon substrate to form a TSV hole with a depth of 550000A;

[0056] 3. SPM cleaning to remove the photoresist on the surface, and LPCVD to deposit a silicon dioxide insulating film 150A;

[0057] 4. Using ion sputtering to grow the barrier layer tantalum nitride 150A, and the seed layer copper 150A;

[0058] 5. Apply photoresist 10000A on the surface of the silicon wafer again, expose, develop, and expose the window that needs copper plating;

[0059] 6. Electroplate copper 650000A on the surface of the silicon wafer, and use SPM to clean and remove the photoresist;

[0060] 7. Using chemical mechanical grinding, grinding to t...

Embodiment 3

[0071] 1. Use Cz silicon (100) (0.1~0.2Ω·cm) substrate; use LPCVD to deposit silicon dioxide 1500A, coat photoresist 10000A on the surface of the silicon wafer, expose and develop, and expose the silicon dioxide with a width of 300000A silicon surface

[0072] 2. Etch silicon dioxide to the surface of the silicon substrate, and continue to etch the silicon substrate to form a TSV hole with a depth of 600000A;

[0073] 3. SPM cleaning to remove the photoresist on the surface, and LPCVD to deposit a silicon dioxide insulating film 150A;

[0074] 4. Using ion sputtering to grow the barrier layer tantalum nitride 150A, and the seed layer copper 150A;

[0075] 5. Apply photoresist 10000A on the surface of the silicon wafer again, expose, develop, and expose the window that needs copper plating;

[0076] 6. Electroplate copper 700000A on the surface of the silicon wafer, and use SPM to clean and remove the photoresist;

[0077] 7. Using chemical mechanical grinding, grinding to t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More